展望2nm工艺的可持续性

随着半导体制造复杂性的不断增加,相关的排放量正在以惊人的速度增长。TechInsights Manufacturing Carbon Module 数据显示,位于俄勒冈州的下一代 2nm 晶圆厂将生产 ~30 万 MtCO2e 每年消耗超过 400 GWh 的电力。鉴于对电力和范围 2 排放的依赖,晶圆厂选址也起着重要作用,位于台湾的同等晶圆厂每年产生的排放量几乎是其三倍。

本文引用地址:https://www.eepw.com.cn/article/202503/468800.htm有胜利。具有高晶体管密度的精细工艺可以大大减少每个晶体管的辐射。半导体制造的碳中和是可能的,但正如我们将要展示的那样,这需要齐心协力,并对可再生能源基础设施进行大量投资。

通往 2nm 之路

英特尔、三星和台积电都有望在未来 12-18 个月内发布下一代 logic 工艺。TechInsights 最近提出了一个技术展望,预计实施方面存在重大差异。

台积电在 IEDM 2024 上详细介绍了其 2nm 工艺。预计将于 2025 年下半年在台湾开始量产。英特尔的等效工艺称为“18A”,也计划在同一时间范围内生产,第一个使用该工艺的产品已经确定——英特尔的下一代 Panther Lake CPU。三星于 2023 年发布了业界首个全能门 (GAA) 工艺,然后在去年发布了量产部件(三星 Galaxy Watch7 的 W1000 处理器)。三星目前计划等到 2026 年发布其 2nm 工艺。

台积电的工艺将成为最密集的,而英特尔则率先推出反向供电 (BSPD) 网络,他们称之为“Power Via”,从而突破极限。三星已经拥有 3nm 的 GAA 经验;如果它的产率足够,理论上可以在将该工艺扩展到 2nm 时提供一些优势。这个下一代节点的独特工艺流程,加上晶圆厂的选址和布置,将影响这些先进工艺对环境的影响。

范围 2 排放和芯片良率的巨大影响

鉴于先进工艺的复杂性和功耗不断增加,两个因素对于减少排放至关重要 - 本地电网碳强度和产量。

对于此处的计算,我们将假设基于位置的电力(即基于晶圆厂位置的电网碳强度)。

从经济学的角度来看,芯片良率至关重要;较低的良率意味着每个晶圆的合格芯片较少,从而增加了生产每个工作芯片的成本。尽管发布了业界首个 GAA 工艺,但三星的 SF3E 和 SF3 仅在相对小批量的市场中出现,并且使用小芯片尺寸。三星 Galaxy S25 系列没有配备三星生产的新 Exynos 处理器这一事实引发了人们对 SF3 工艺良率是否足够高以应对该应用的处理器尺寸和体积的问题。虽然低良率意味着每个芯片的成本更高,但碳排放也是如此。

从 TechInsights Manufacturing Carbon Module 获取数据,我们来分析一些具体的例子。由于晶圆厂在不同的时间上线,具有不同的吞吐量,并且具有不同的供应链,因此很难进行同类比较。因此,鉴于 2nm 工艺需要几年时间才能完全达到峰值产能,让我们展望 2028 年;此时,3nm 和 2nm 都将是大批量运行的成熟工艺。

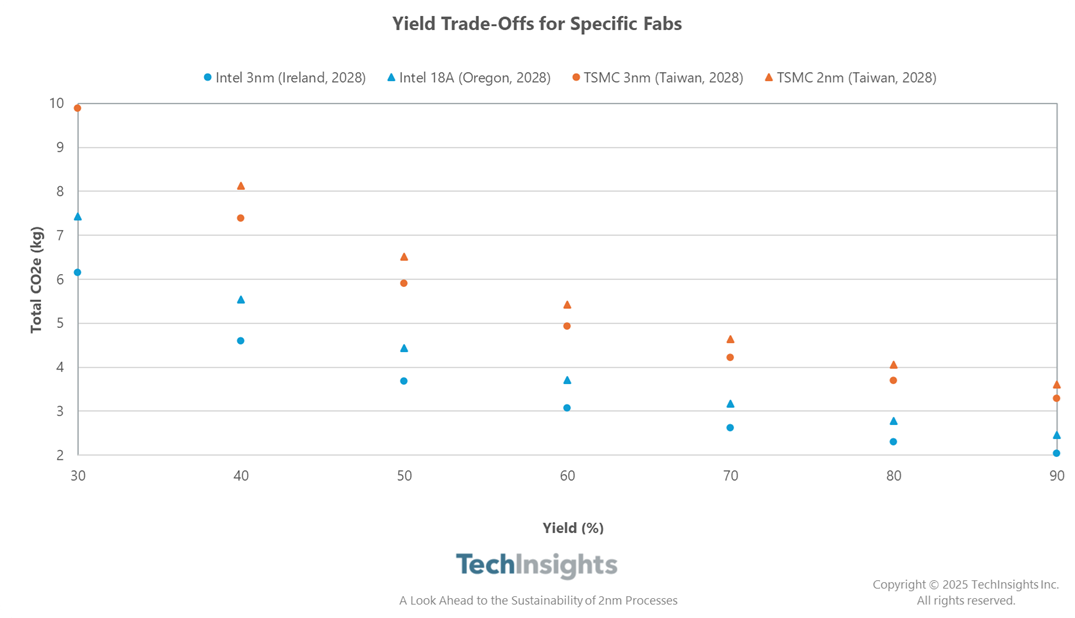

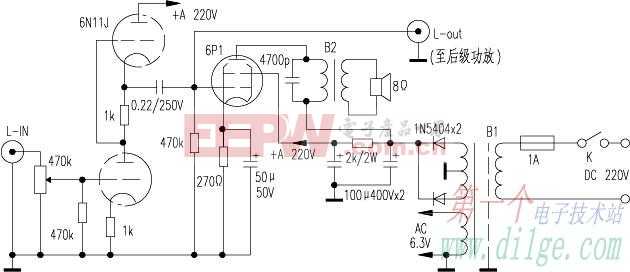

图 1 比较了电网碳强度的两种相反的极端情景,以英特尔和台积电的晶圆厂为例,它们应该都在今年投入生产,并在 2028 年之前全面投产。

特定Fabs.png的收益权衡

特定Fabs.png的收益权衡

图 1 比较具有不同本地电网碳强度的先进逻辑工艺。来源:TechInsights Manufacturing Carbon Module,2025 年

英特尔具有固有的电力优势,因为其 3nm 和 18A 工艺将在爱尔兰和美国俄勒冈州相对低碳的电网中制造。

台积电至少在最初将遭受台湾可再生能源挑战,正如去年在深入的 TechInsights 分析中所讨论的那样。虽然 2nm 最终可能会在亚利桑那州台积电生产,但可能需要 2030 年才能实现。到 2028 年,台湾电网碳强度仍有望达到爱尔兰或俄勒冈州的 2 倍以上。

与此同时,如果历史是一个很好的指标,预计台积电将有非常好的收益率,而对英特尔近期收益率的信心较低。正如 TechInsights 2nm 技术展望中所讨论的那样,一些消息来源表明英特尔的 18A 良率低至 10%。在 TechInsights,我们认为这不太可能,而且当芯片制造商开始量产时,它的产量肯定会显着提高。尽管如此,英特尔与生俱来的电网优势意味着,即使英特尔的 18A 在其俄勒冈州工厂的产量仅为 60%,这仍然会产生与台湾台积电 2nm 工艺相似的排放,即 90%。换句话说,如果两个工艺的产量均为 90%,那么台积电 2nm Taiwan 工艺的排放量将增加 47%。

哪种下一代制造工艺最可持续?

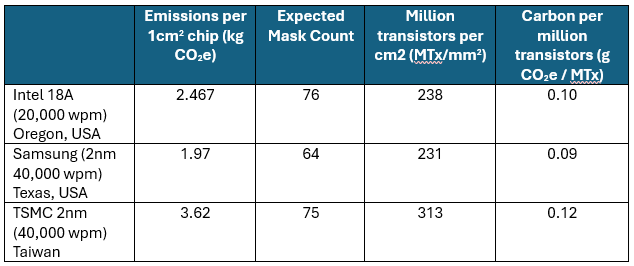

三星呢?韩国的电网碳强度略好于台湾,但仍是俄勒冈州的两倍多。然而,三星正在德克萨斯州泰勒建造一座先进的工厂,到 2026 年底可以生产 2nm。因此,现在让我们切换到“2028 年最佳情况”,假设收益率为 90%。谁是赢家?表 1 显示了一些重要的权衡。

表 1.2028 年代工厂生产 2nm 芯片的最佳情况。来源:TechInsights 的制造碳模块,2025 年。

在这种情况下,三星在每芯片的基础上获胜,因为德克萨斯州的电网碳强度较低,而三星工艺的掩模数量较少。

如果我们以按晶体管缩放的方式看待事物,就会发生一个有趣的平衡。

TechInsights 对所有 2nm 等效工艺进行了晶体管逻辑密度计算,并认为它们如下:高密度逻辑单元晶体管密度为 313 MTx/mm2用于台积电,238 MTx/mm2适用于 Intel,以及 231 Mtx/mm2对于三星。由此,我们还可以计算出 CO2e/MTx 的数字。在这种情况下,三星仍然获胜。然而,情况要接近得多,由于晶体管密度高于三星工艺,台积电更具竞争力。

这些结果仍应被视为初步的预期;所有过程都仍然存在问题。在撰写本文时,尽管台积电台湾工艺的排放量最高,但它似乎确实是最有可能按计划进行的过程。据报道,三星的德克萨斯州项目与英特尔的项目一样,产量较低。假设亚利桑那州的台积电 2nm 工艺在本世纪末加速发展。在这种情况下,台积电也将受益于美国较低的网格强度,而这一工艺,再加上其增加的晶体管密度,将成为巨大的赢家。

2nm 实现碳中和需要什么?

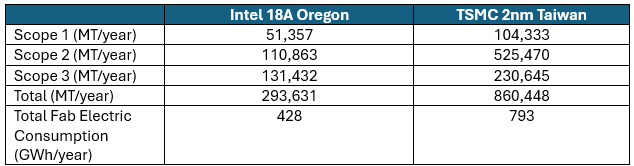

作为最后一个思想实验 - 如何使 2nm 等效晶圆厂完全碳中和?让我们回到 2028 年俄勒冈州的 Intel 18A 和 TSMC 2nm 的初步例子。表 2 细分了每个晶圆厂一年的排放量。

表 2.按范围划分的晶圆厂每年碳排放总量。来源:TechInsights 的制造碳模块,2025 年。

在台湾的例子中,范围 2 排放占主导地位;然而,Intel 发生了一些奇怪的事情。尽管具有与 TSMC 工艺相似数量的掩模,但涉及 EUV 光刻的掩模要少得多。(我们估计英特尔芯片有 17 个掩码,而台积电有 24 个掩码。BSPD 的实现允许在 Mx 层中实现宽松的间距,并减少多重图形化)。这意味着范围 2 的贡献要低得多,尽管仍占总数的 38%。

范围 2,即与电力消耗相关的间接排放,是指安装可再生能源(如太阳能)可能会直接影响排放的地方。这将抵消英特尔晶圆厂每年使用的 428 GWh 总量多少?

假设这家英特尔工厂所在的俄勒冈州地区的太阳能发电容量系数为 20%,那么 1 MW 的太阳能光伏装机容量每年将产生 1.752 GWh 的发电量。因此,需要一个 244 MW 的太阳能光伏装置来抵消该工厂的电力消耗。就所需的土地面积而言,这相当于大约 12.5 公里2数组。台湾的台积电的太阳能容量系数较低,鉴于耗电量较高,与俄勒冈州的英特尔相比,总共需要大约三倍的装机容量。

当然,范围 2 只占故事的 38%。虽然范围 1 排放量已经相对较低(我们估计该晶圆厂的气体减排量为 98%),但剩余的 2% 将极具挑战性,甚至可能无法以今天的技术减排。因此,碳中和的唯一途径可能是使用碳抵消。范围 3 也很复杂,需要在整个供应链中保持一致。如果我们要对剩余的 18 万 MtCO 尝试抵消方法2,环境保护署 (EPA) 的数据显示,这相当于近 200,000 英亩(~8,00 平方公里) 美国森林一年的封存碳价值)。在 TechInsights 对 Apple 寻求碳中和的分析中,我们讨论了其实现碳中和的碳抵消方法,显示抵消这些排放水平是可能的,但并不简单。

这些问题不仅对晶圆厂的报告目的很重要,而且对整个供应链(即无晶圆厂半导体公司或产品制造商)也很重要。这将继续推动整个半导体价值链合作,并在控制先进半导体制造排放方面取得有意义的进展。故事并没有就此结束;正如最近的 TechInsights 分析中所讨论的那样,2nm 将使用额外的水和含 PFAS 的化学品。

(注:本文登于EEPW 202504期)

评论