GD32F103替换STM32F103需要注意的地方

查了下GD的手册和一些论坛中使用过的大佬发布的帖子,GD32F103替换STM32F103需要注意的地方总结如下:

本文引用地址:https://www.eepw.com.cn/article/202401/455180.htm一、相同点

1) 、外围引脚定义: 相同型号的管脚定义相同

2) 、Cortex M3 内核: STM32F103 内核 R1P1 版本, STM32F205 内核 R2P1, GD32 内核 R2P1 版本,此内核已经修复了 R1P1 的一些 bug

3)、 芯片内部寄存器, 外部 IP 寄存器地址 : 逻辑地址相同,主要是根据 STM32 的寄存器和物理地址,做得正向研发.

4) 、函数库文件: 函数库相同,优化需要更改头文件

5) 、编译工具: 完全相同 例如:keil MDK、IAR

6)、 型号命名方式: 完全相同

二、外围硬件区别

1) 、电压范围(ADC): GD32F: 2.6-3.6V STM32F: 2.0-3.6V(外部电压) GD32F: 1.2V(内核电压)STM32F: 1.8V(内核电压)

2)、 BOOT 0 管脚: Flash 程序运行时,BOOT0 在 STM32 上可悬空,GD32 必须外部下拉(从 Flash 运行,BOOT0 必须下拉地)

3)、 ESD 参数: STM32 人体模式 2KV,空气模式 500V GD32 人体模式 4KV(内测 5KV),空气模式 10KV(内测 15KV)

三. 内部结构差别

1) 、启动时间: GD32 启动时间相同,由于 GD 运行稍快,需要延长上电时间 配置(2ms)

2) 、主频时钟: GD32F10 系列主频 108MHZ STM32F10 系列主频 72MHZ

3)、 Flash 擦除时间: GD32 是 60ms/page,STM 30ms/page

4) 、FLASH 容量: GD32 最大容量 3M Byte

5)、 SRAM 空间: GD32F103 系列、GD32F105107 大容量系列 SRAM 96K

6)、 VB 外扩总线 FSMC:GD32 100PIN 配置总线输出,STM32 144PIN 并且 256k 以上 才配置总线输出

四. 功耗区别(以 128k 以下容量的作为参考)

1) 、睡眠模式 Sleep: GD32F: 12.4mA STM32F10X: 7.5mA

2) 、深度睡眠模式 Deep Sleep: GD32F: 1.4mA STM32F10X: 24uA

3)、 待机模式 Stand By: GD32F: 10.5uA STM32F10X: 3.4uA

4) 、运行功耗: GD32F: 32.4mA/72M STM32F10X: 52mA/72M

五、硬件替换要注意的地方

从上面的介绍中,我们可以看出,GD32F103系列和STM32F103系列是兼容的,但也需要一些注意的地方。

1、BOOT0必须接10K下拉或接GND,ST可悬空,这点很重要。

2、RC复位电路必须要有,否则MCU可能不能正常工作,ST的有时候可以不要。

3、有时候发现用仿真器连接不上。因为GD的swd接口驱动能力比ST弱,可以有如下几种方式解决:

a、线尽可能短一些;

b、降低SWD通讯速率;

c、SWDIO接10k上拉,SWCLK接10k下拉。

4、使用电池供电等,注意GD的工作电压,例如跌落到2.0V~2.6V区间,ST还能工作,GD可能无法启动或工作异常。

四、使用ST标准库开发需要修改的地方

1、GD对时序要求严格,配置外设需要先打开时钟,再进行外设配置,否则可能导致外设无法配置成功;ST的可以先配置在开时钟。

2、修改外部晶振起振超时时间,不用外部晶振可跳过这步。

原因:GD与ST的启动时间存在差异,为了让GD MCU更准确复位。

修改:

将宏定义:#define HSE_STARTUP_TIMEOUT ((uint16_t)0x0500)修改为:#define HSE_STARTUP_TIMEOUT ((uint16_t)0xFFFF)

3、GD32F10X flash取值零等待,而ST需要2个等待周期,因此,一些精确延时或者模拟IIC或SPI的代码可能需要修改。

原因:GD32采用专利技术提高了相同工作频率下的代码执行速度。

修改:如果使用for或while循环做精确定时的,定时会由于代码执行速度加快而使循环的时间变短,因此需要仿真重新计算设计延时。使用Timer定时器无影响。

4、在代码中设置读保护,如果使用外部工具读保护比如JFLASH或脱机烧录器设置,可跳过此步骤。

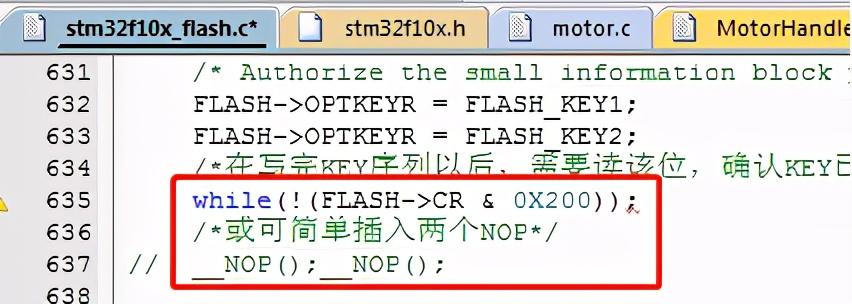

在写完KEY序列后,需要读该位确认key已生效,修改如下:

总共需要修改如下四个函数:

FLASH_Status FLASH_EraseOptionBytes(void);FLASH_Status FLASH_ProgramOptionByteData(uint32_t Address, uint8_t Data);uint32_t FLASH_GetWriteProtectionOptionByte(void);FlagStatus FLASH_GetReadOutProtectionStatus(void);

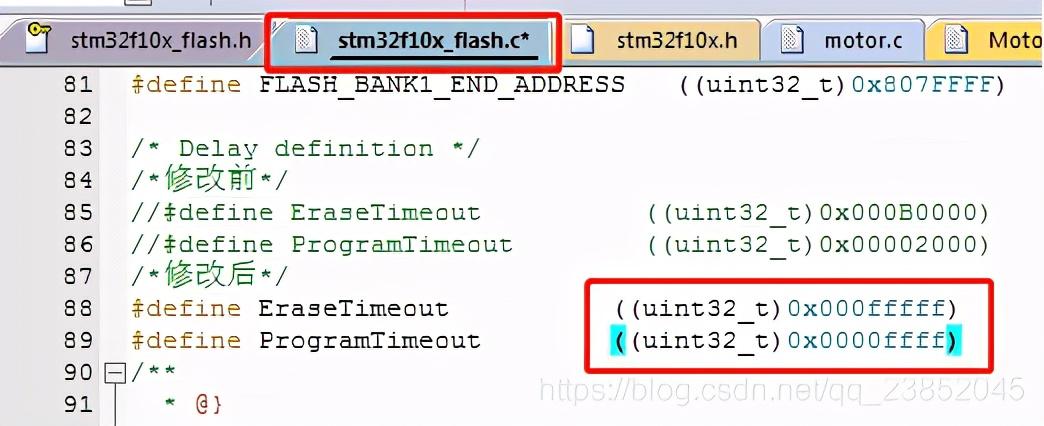

5、GD与ST在flash的Erase和Program时间上有差异,修改如下:

6、需求flash大于256K注意,小于256K可以忽略这项。

与ST不同,GD的flash存在分区的概念,前256K,CPU执行指令零等待,称code区,此范围外称为dataZ区。两者在擦写操作上没有区别,但在读操作时间上存在较大差别,code区代码取值零等待,data区执行代码有较大延迟,代码执行效率比code区慢一个数量级,因此data区通常不建议运行对实时性要求高的代码,为解决这个问题,可以使用分散加载的方法,比如把初始化代码,图片代码等放到data区。

7、ADC采集

a> ADC通道要配置成模拟输入,芯片默认是浮空输入,如果不配成模拟输入,ST的可以正常采集,GD不行

b> ADC时钟没有手动分频最大运行频率14Mhz以内,ST可以正常采集,GD不行。

c> ADC使能后需要加不少于20us延时。

d> 采样精度不如STM32f103,GD32f103存在这个问题,如果对ADC精度要求不高可以选用,可以选用PIN TO PIN 兼容F103系列的GD32E103和GD32F303系列解决。

总结:至此,经过以上修改,不使用USB和网络等复杂协议的代码,就可以使用ST的代码操作了。

PS:GD的主频支持108MHz,有时候需要提供主频,提供一个96MHZ的参考:

static void SetSysClockTo96(void){

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

RCC_APB2PeriphResetCmd(RCC_APB2Periph_AFIO|RCC_APB2Periph_GPIOA|RCC_APB2Periph_GPIOE|RCC_APB2Periph_GPIOC,ENABLE);

RCC_APB2PeriphResetCmd(RCC_APB2Periph_AFIO|RCC_APB2Periph_GPIOA|RCC_APB2Periph_GPIOE|RCC_APB2Periph_GPIOC,!ENABLE);

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/* Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/* Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));for(StartUpCounter=0;StartUpCounter<0x1fff;StartUpCounter++); if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

} else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{ /* Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE; /* Flash 2 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;#ifdef STM32F10X_CL

/* Configure PLLs ------------------------------------------------------*/

/* PLL2 configuration: PLL2CLK = (HSE / 5) * 8 = 40 MHz */

/* PREDIV1 configuration: PREDIV1CLK = PLL2 / 5 = 8 MHz */

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV5);

/* Enable PLL2 */

RCC->CR |= RCC_CR_PLL2ON; /* Wait till PLL2 is ready */

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

/* PLL configuration: PLLCLK = PREDIV1 * 12 = 96 MHz */

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL12);

#else #if 0

/* PLL configuration: PLLCLK = HSE * 12 = 96 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL)); for(StartUpCounter=0;StartUpCounter<0x1fff;StartUpCounter++);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL12);#else// RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |// RCC_CFGR_PLLMULL));

//RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE|(1<<17));

//RCC->CFGR &= ~(RCC_CFGR_PLLMULL);

//RCC->CFGR |= (uint32_t)(1<<27u);

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | (1<<27)|(7<<18)|(1<<17));#endif#endif /* STM32F10X_CL */

/* Enable PLL */

RCC->CR |= RCC_CR_PLLON; /* Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

} for(StartUpCounter=0;StartUpCounter<0x1fff;StartUpCounter++); /* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

for(StartUpCounter=0;StartUpCounter<0x200;StartUpCounter++); for(StartUpCounter=0;StartUpCounter<0x1fff;StartUpCounter++); /* Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

} else

{ /* If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

}

}还是希望国产芯片能越做越好,早日实现国产化,这样就不怕人家卡脖子了!

评论