TD-LTE射频一致性测试系统数字中频单元设计

在FPGA中实现半带滤波器与CIC滤波器,RAM资源消耗为零,且乘法器、查找表与寄存器消耗较少,具体资源分布情况如表2所示。

本文引用地址:https://www.eepw.com.cn/article/192732.htm高速串行接口设计

LTE基带信号数据吞吐量较大。本设计根据串行RapidIO协议在FPGA中,分别例化一个4X的SRIO(Serial-RapidIO)核用于基带板和数字中频板之间连接,同时例化1个1X的SRIO核用于数字中频板内部FPGA与DSP连接。

测试例功能模块设计

TS 36.521-1测量规范定义了LTE终端的发射机测试、接收机测试和性能测试的过程和测量方法。其中,终端发射机测试内容包括:(1)开环功率测量(OLP);(2)闭环功率控制(TPC步进量:1/2/3dB);(3)最大/小输出功率测试(APC);(4)关断功率测试(PVT);(5)发射/关断时间模板(ECTM);(6)频率误差(FE);(7)误差矢量幅度(EVM);(8)邻道泄漏抑制比(ACLR);(9)占用带宽(OBW);(10)频谱发射模板(SEM)。

以上测试内容中,第1、2、3、4测试项由FPGA独立完成;第5、6、7、8、9、10测试项FPGA作为预处理器,再由DSP处理后续复杂算法。

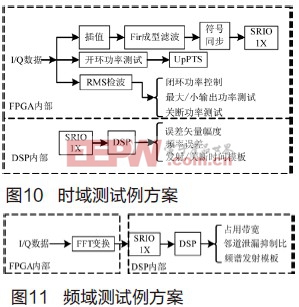

本设计测试例功能方案分时域、频域处理两部分,时域、频域处理流程如图10、11所示。

插值、成型滤波与符号同步子模块设计

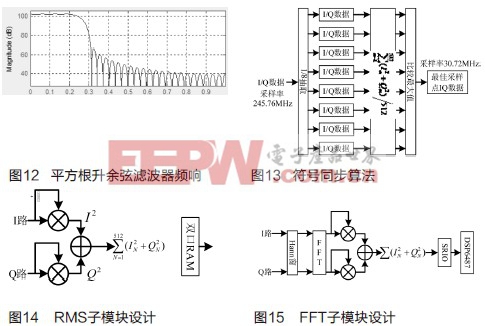

该模块插值选用CIC插值器,差值倍数为8倍。成型滤波选取“平方根升余弦”FIR,符号同步采用“平均功率最大值”算法。平方根升余弦滚降因子选0.22,FIR阶数为96阶,频响曲线如图12所示。

FPGA中符号同步算法流程图如图13所示。

RMS子模块设计

闭环功率控制测试、最大/小功率测试、关断功率(PVT)测试和开环功率测试等模块的检波方式为“方均根”检波(Root Mean Square),RMS定义如下:

xi表示某一时刻数据,N表示任一个连续取值的个数。由公式(15)可知,离散/数字信号的方均根(RMS)定义本身包含着“积分”概念,积分后的信号曲线有“平滑”的效果。该子模块FPGA设计如图14所示。

在FPGA中方均根检波后,功率信号为I2+Q2,以此信号为基准,设计逻辑电路捕获脉冲信号并保存至双口RAM中,上位机主控软件从RAM中获取数据进行对数(logarithm)处理并显示。

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

模数转换器相关文章:模数转换器工作原理

数字滤波器相关文章:数字滤波器原理

评论