FPGA深层解析

SCTL

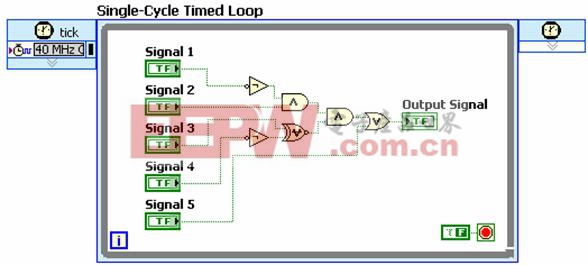

上几节中使用的代码例子假定代码是设置在SCTL外部,并为保证执行同步数据量也同步了附加电路。SCTL是LabVIEW FPGA中一个特殊结构,生成一个更为优化的电路图,以期望达到在一个时钟(脉冲)周期内执行完所有逻辑电路分支。例如,若设置SCTL在40MHZ运行,则所有逻辑电路分支将在25ns内执行完毕。

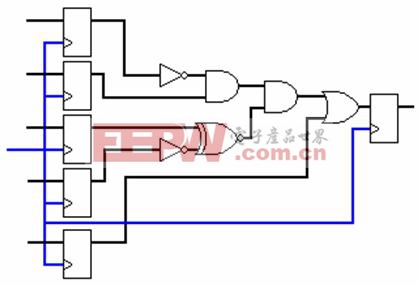

如果在SCTL中设置前例中同样的布尔逻辑电路(如图9所示),则生成如图10所示的相应电路示意图。

图9.附有STCL的简单布尔逻辑

图10.图9所示布尔逻辑相应的电路图

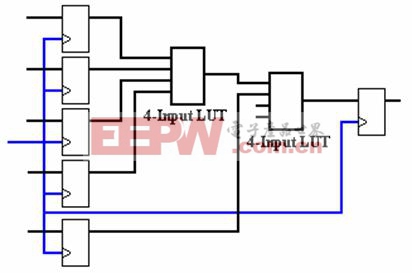

很明显,这种实现方法简单多了。在Virtex-II或Spartan-3系列FPGA中,触发器间的逻辑需要至少2个4输入查找表,如图11所示。

图11.图10中电路图的双四输入查找表实现

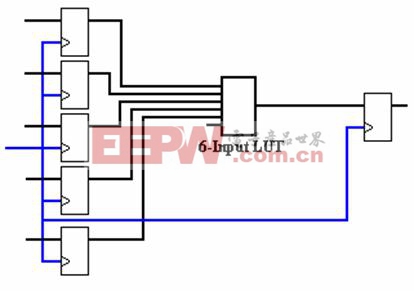

由于Virtex-5系列FPGA有着6输入的查找表,用户可以在一个查找表中实现相同数量的逻辑,如图12所示。

图12.图10中双六输入查找表实

本例中使用的SCTL(如图9所示)设置在40MHZ下运行,这意味着在任意触发器之间逻辑电路必须在25ns内完成执行。电子在电路中传播的速度决定了代码执行的最大速度。关键路线是有最长传播延迟的逻辑电路分支,它决定了该部分电路中理论最大时钟速率。Virtex-5 FPGA上的双六输入查找表不仅减少实现给定逻辑电路所需要的查找表总数,而且减少电子通过逻辑电路的传播延迟(时间)。Virtex-5系列FPGA中的6输入查找表不仅可以减少实现特定逻辑而需要的查找表的数量,而且可以降低逻辑中电流的传输延时。这意味着,您可简单地通过选择一个基于Virtex-5的硬件指标设置相同的SCTL,追求更快的时间速度。

评论