成功解决FPGA设计时序问题的三大要点

FPGA的设计与高速接口技术可以帮助你满足今天的市场要求,但也提出了一些有趣的设计挑战。为了确保存储器接口的数据传输准确,在超过200兆赫兹以上,进行时序分析将发挥更突出的作用,以识别和解决系统运行的问题。在这些频率内,最重要的是创建和控制时序空余,留下最小的空余,以确保数据采集和演示窗口的准确。更快的边缘速率同时也放大物理设计的影响,造成信号完整性问题,对此则需要更多的沉降时间及缩小时序空余。

本文引用地址:https://www.eepw.com.cn/article/192059.htmFPGA器件现在还包括某些先进的功能,如支持带有I/O单元接口的双通道数据(DDR)和板上锁相环(PLL)网络进行精确时钟控制等等。这些在FPGA技术中的高级功能均提供先进的接口模块,从而有助于减少界面设计,再加上TimingDesigner软件的独特能力,在最短的时序中提供最准确、有力的解决方案。本文主要探讨了DDR型存储器接口设计中必要的时钟偏移及数据采集的时序空余。

DDR/QDR存储器接口的设计问题

DDR或四倍数据速率(QDR)存储设备可以提供和接受两倍于器件时钟频率的源同步数据,这意味着数据在时钟的上升缘和下降缘传输。此外,需要捕捉时钟偏移和进行适当地调整,以确保适当的时钟与数据关系。

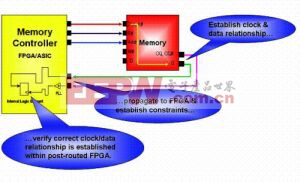

图1:TimingDesigner软件便于捕获设计特点的图形界面窗口。

如前所述,现在一些FPGA装置包括DDR接口的I/O单元和板上的PLL网络。这意味着,你必须有一个方式来控制模块的准确和可靠。为了说明这一点,让我们来读取QDR II SRAM源同步接口的设计要求看看实例。

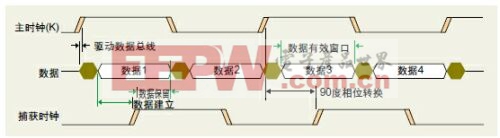

在同步存储器系统例如QDR SRAM中,数据是与时钟同步的,所以存储器数据的相位必须旋转90度。这种相位旋转通常在有效数据窗口中进行时钟中心调整,这是QDR实现准确数据采集的一个重要设计特点(见图2)。如果要改变时钟中心,我们可以通过对板上FPGA的PLL网络进行简单的延时时钟信号来达到。

图2:中心对齐的时钟/数据关系。

评论