基于单片机和FPGA的网络数据加密实现

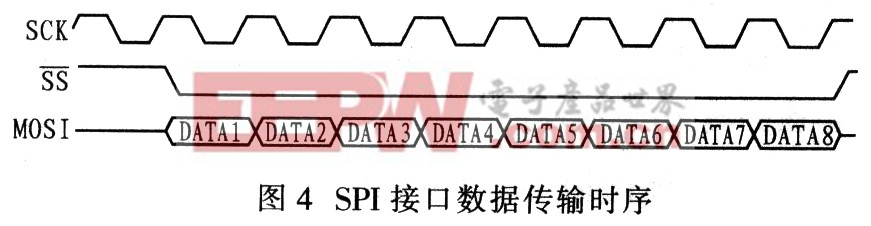

由于TI公司的MSP430系列微处理器平台具有低功耗和小体积等特点,适合便携式应用场合,所以单片机采用MSP430系列,并通过SPI接口实现与FPGA的数据通信。单片机外接一键盘,用于输入初始密钥。考虑到用户输入密钥位数不能很多,可设置简短的密钥,并在单片机内部扩展至算法所需的位数,然后通过单片机SPI接口传送至FGPA。SPI接口共4条信号线:串行时钟(SCK),主机输出/从机输入(MOSI),主机输入/从机输出(MISO),从机片选(SS)。SPI接口可配置为主或从模式。设计配置为主模式。当单片机向FPGA传输命令或数据时,应用SPIO模式。当片选信号丙拉低,在每个时钟(SCK)的上升沿发送数据,无需FPGA向单片机输人数据,所以不使用MISO数据线。片选信号SS与FP-CA的RAM的使能相连,控制数据读入。当用户输人初始密钥后,经过数据扩展,与算法选择数据通过SPI接口传送至FPGA。SPI接口时序如图4所示。本文引用地址:https://www.eepw.com.cn/article/192015.htm

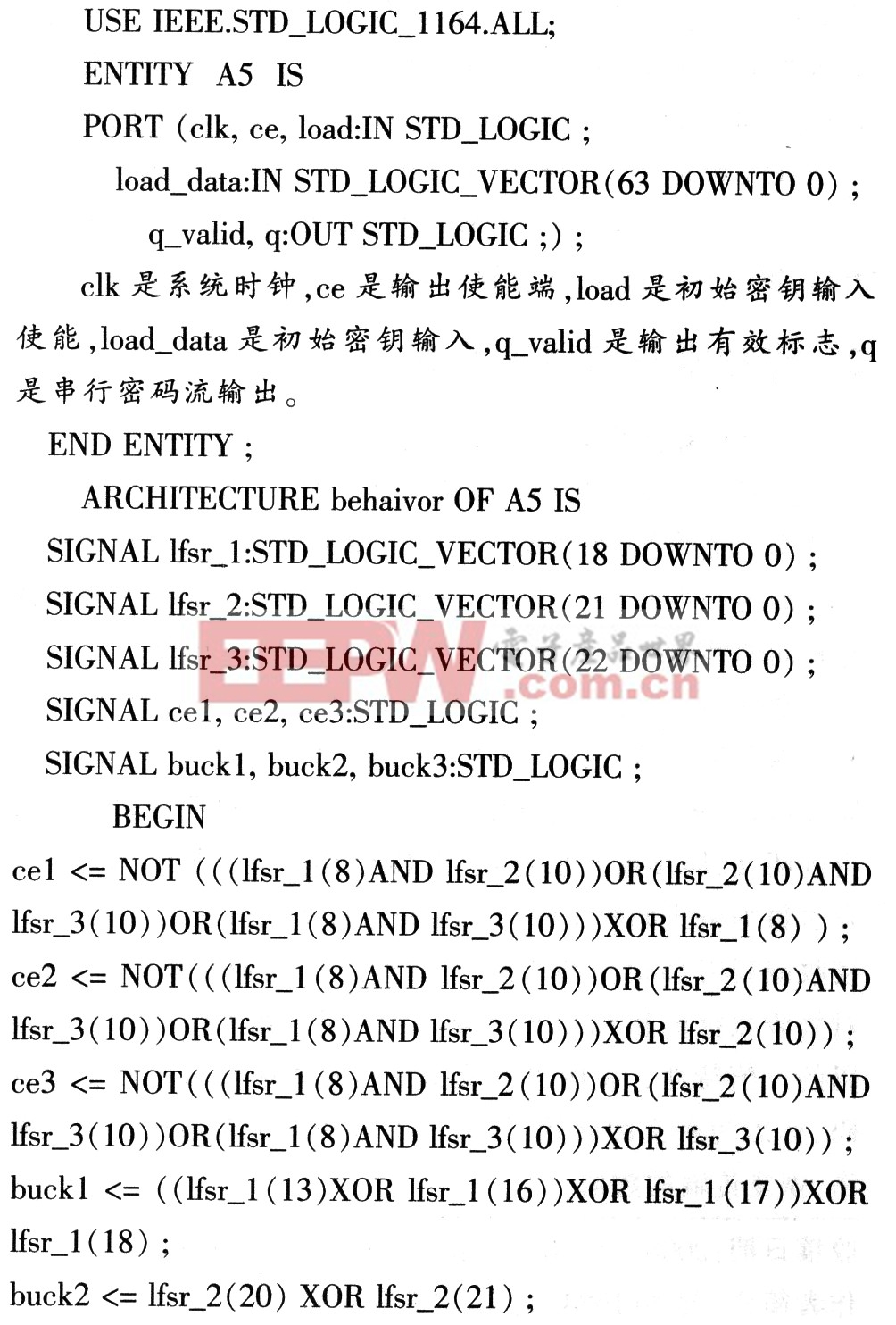

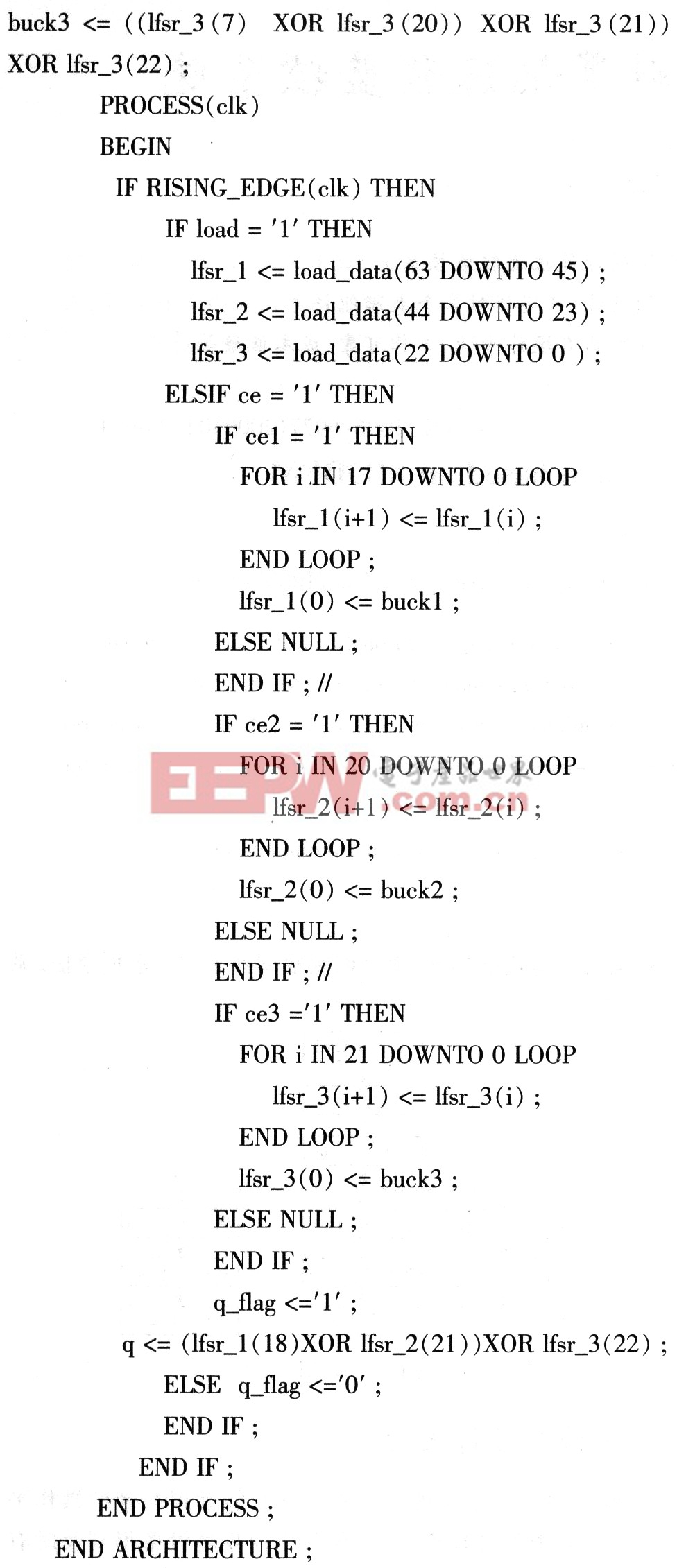

FPGA采用CyeloneII系列中的EP20F256C6,该器件是低成本架构FPGA,可提供多达18 752个逻辑单元.152个用户IO,239 616 bit的存储位,密度超过CyeloneI FPGA的3倍,完全满足系统设计需要。CycloneII FPGA内部的逻辑资源可实现复杂应用。CyeloneII器件采用的低成本串行配置器件,这种串行配置器件最大可提供64 Mbit的nash存储器。所以,采用EP20F256C6可高效完成系统核心算法,有效节约成本。其内部算法由VHDL语言编程实现。主要程序模块:加解密算法模块(A5/1和W7)、数据存储模块、同步产生模块、同步检测模块。加密和解密各有一套独立的模块集合。其中A5/1算法模块的VHDL代码如下:

pos机相关文章:pos机原理

评论