基于FPGA的双口RAM与PCI9O52接口设计

当状态机处于读空闲状态时,在每次上升沿采样到ADS有效和LW R为低电平,且访问双口RAM空间(CS0或CSl有效),状态机转到读开始状态。接着是读等待数据状态,此时根据片选信号CS0和CSl的值译出SEML、CE0L、CElL,并输出有效的地址和控制信号R WL、UBL、LBL、OEL到双口RAM。接着是读过程状态,为了得到有效的数据,该过程未对输入输出操作。然后是读过程等待状态,此时,置LRDY信号有效且输出有效的数据到PCI9052。最后是写结束状态,在该过程的下一个周期将读控制信号置为无效,状态机恢复为读空闲状态。本文引用地址:https://www.eepw.com.cn/article/191746.htm

3 FPGA仿真实现

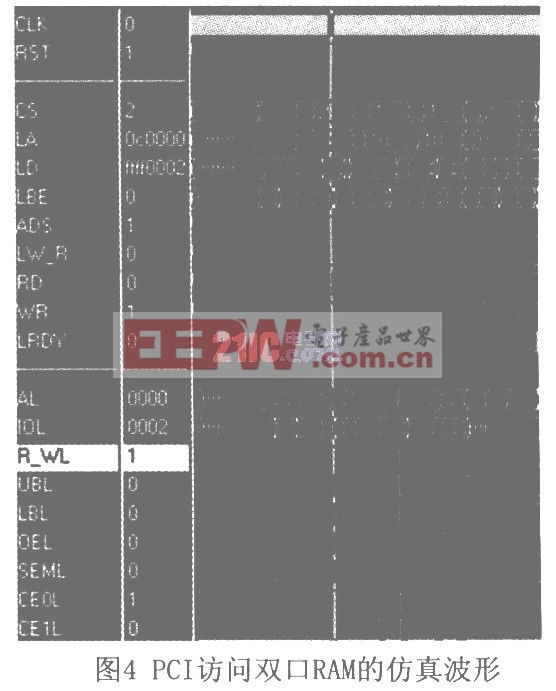

在Modelsim开发平台下,实现了PCI9052读写双口RAM的仿真过程,该仿真波形如图4所示。从仿真波形可以看出该代码可以实现将PCI90-52的读写控制信号转换成双口RAM的读写控制信号,完成时序的匹配。

4 结语

本设计采用了可编程逻辑芯片来实现PCI访问双口RAM的接口电路,该接口电路具有可改性与适用性。随着微电子技术的发展,可编程器件的容量已经达到千万门级,越来越多过去必须由专用芯片或器件才能完成的工作现在都可以通过设计软件由FPGA来实现了。硬件的软件化已经成为电子行业中不可阻挡的趋势。

评论