基于FPGA的图像裁剪电路的设计与实现

摘要:本文提出了一种基于FPGA的图像裁剪电路的设计方法,利用像素的抽取改变图像的分辨率,从而达到图像裁剪的效果。与传统的方法相比,这种方法简单易行,开发成本低,图像的清晰度能满足一定的要求。此方法数据处理速度快,尤其适用于动态图像的处理。

关键词:现场可编程门阵列:图像裁剪;分辨率

0 概述

图像处理电路是信息控制系统中必不可少的环节,广泛应用于生产生活中,如住宅小区的安全监控系统、生产线的质量监控系统、电视机的机顶盒等,因此图像的处理电路的开发受到了人们的重视。裁剪压缩是图像处理技术中一个重要的内容,传统的方法往往采用DSP芯片或插值算法来实现图像的裁剪压缩功能,这种方法存在电路设计复杂、开发成本高的问题。本文提出了一种基于FPGA的设计方法,利用像素的抽取改变图像的分辨率,从而达到图像裁剪的效果。这种设计方法简单易行,图像的清晰度能满足一定的要求。特别是由于不需要数学运算,所以此方法数据处理速度快,尤其适用于一般要求的动态图像的处理。

1 电路设计方案

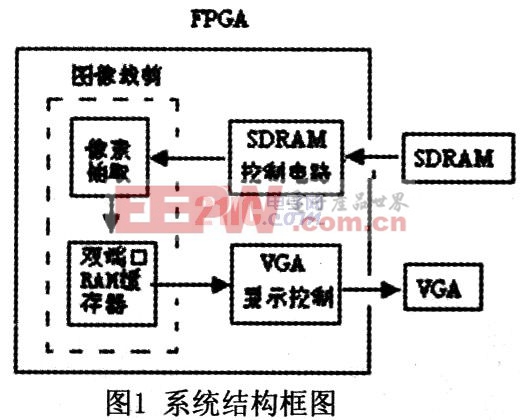

本设计是一个基于FPGA的数字图像的裁剪电路,电路框图如图1所示。其中FPGA中包含了三个功能模块电路的设计:

(1)SDRAM的控制模块:预处理的图像存在SDRAM存储器中,通过SDRAM的控制模块,将图像信息读出并进行相应的处理,提供给下一个电路模块使用。

(2)图像裁剪电路:包括像素的抽取和缓存电路,采用改变图像分辨率的方法,将有效的像素提取出来提供给显示电路,使图像进行4:3或2:3等多比例变化,以达到不同的视觉效果。

(3)显示控制电路:根据VGA显示屏的特点,产生时序驱动信号控制图像数据显示。

DIY机械键盘相关社区:机械键盘DIY

评论