基于FPGA的任意波形发生器设计与实现

3 系统软件设计与实现

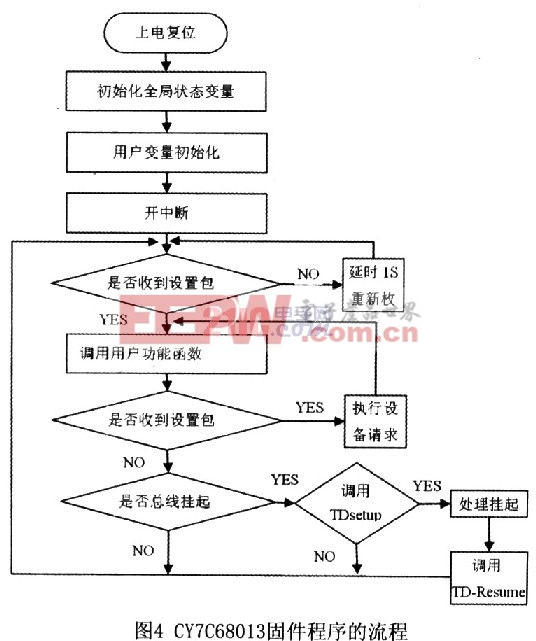

3.1 固件程序设计

CY7C68013内嵌有8051微处理器,用于控制芯片的工作状态设置,写入微处理器的程序文件称为固件程序(Firmware),为了便于维护和移植,一般采用单片机的C语言编写。主要有以下几种功能:a.初始化工作,包括设置一些特殊功能寄存器的初值以实现所需的设备属性或者功能,例如开中断、使能端点、配置端口等。b.辅助硬件完成设备的重新列举过程,包括模拟设备的断开与重新连接,对接收到的设置包进行分析判断,从而对主机的设备请求作出适当的响应,完成主机对设备的配置任务。c.对中断的处理。d.数据的接收和发送。e.外围电路的控制。固件程序的流程如图4所示。

3.2 FPGA程序设计

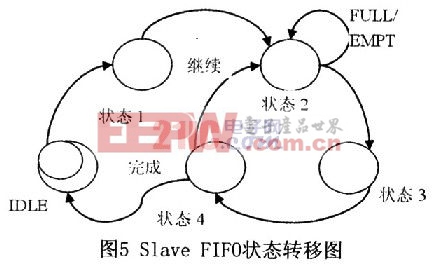

在本系统中FPGA作为主控制器,提供USB控制、DA控制、SRAM控制、I2C控制及全局时钟控制等功能模块。这里重点介绍USB接口控制模块。固化程序将CY7C68013A设置为Slave FIFO工作模式,需要FPGA提供FIFO端口的读写操作控制时序。CY7C68013A为每个端口提供了”空”标志、”满”标志和”可编程级”标志。FPGA检测这些信号,用于控制读写的过程,FPGA再完成这些端口FIFO的操作时序控制。USB控制器的状态转移如图5所示,控制器工作在五个状态中,上电复位后工作在IDLE状态,当读/写事件发生时进入状态1;在状态1中根据读/写事件使能FIFOADR[1:0]指向相应FIFO并进入状态2;在状态2,如果FIFO空/满,在当前状态等待,否则进入状态3;在状态3中,驱动数据总线,完成读/写操作,进入状态4;在状态4中,如需传输更多数据,进入状态2,否则进入状态IDLE。本系统采用Verilog HDL硬件描述语言实现了FIFO的读写时序,并在ALTERA公司提供的QuartusII8.0开发工具中综合编译并映射到FPGA中运行。

4 结果及分析

在设计结果中,最后的波形图是使用泰克公司的TDSl012型示波器得到的。经过实际的测试,该信号发生器产生的波形精度高、失真小,完全满足设计的要求。图6是产生的正弦波、锯齿波的波形结果。

评论