基于FPGA的任意波形发生器设计与实现

(3)数据存储芯片SRAM。考虑到成本的因素,本系统采用ISSI公司的IS6lLV25616-10T。

(4)D/A转换芯片。本设计使用的是AD9726,该芯片控制信号简单,D/A转换速度快,因此将系统的硬件设计大为简化,也减轻了系统软件设计的工作量。

(5)FPGA控制芯片。本设计使用的是Altera公司的Cyclone II系列型号为EP2C20F484的FPGA。EP2C20F484以90nm工艺技术为基础,提供了18,752个逻辑单元(LE),并具有一整套最佳的功能,包括嵌入式18位×18位乘法器、专用外部存储器接口电路、4kbit嵌入式存储器块、锁相环(PLL)和高速差分I/O能力等。本文引用地址:https://www.eepw.com.cn/article/191658.htm

2 系统功能及硬件实现

2.1 USB传输模块

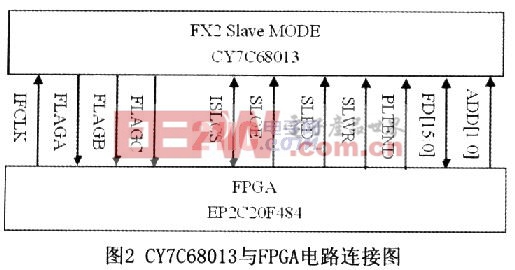

CY7C68013有2种接口方式:Slave FIFOs和可编程接口GPIF。当FPGA与其相连时,只需要利用CY7C68013作为一个USB2.0数据通道来实现与主机的高速通信。

Slave FIFOs方式是从机方式,外部控制器可像普通FIFO一样对CY7C68013的多层缓冲FIFO进行读写。CY7C68013的Slave FIFOs工作方式可设为同步或异步;工作时钟可选为内部产生或外部输入,其它控制信号也可灵活地设置为高有效或低有效。电路连接图如图2所示。

IFCLK是同步时钟信号,FLAGA、FLAGB和FLAGC是CY7C68013内部FIFO的状态标志,EP2C20F484通过通用I/O口获得CY7C68013内部FIFO的空、半满(由用户设定半满阈值)和满这三个状态信号,ISLCS、SLOE、SLRD、SLWR对CY7C680l3进行读写操作控制,FD[15:0]是数据线,ADD[1:0]是选择4个FIFO的地址线。其工作过程为:PC机通过USB向FPGAP发送波形数据时,USB通过请求方式通知FPGA读取波形数据,FPGA首先查看空、半满和满这三个状态信号,选择一个FIFO,然后控制USB接收适当大小的数据,以保证数据不会溢出,并存入SRAM中。

2.2 DAC功能模块

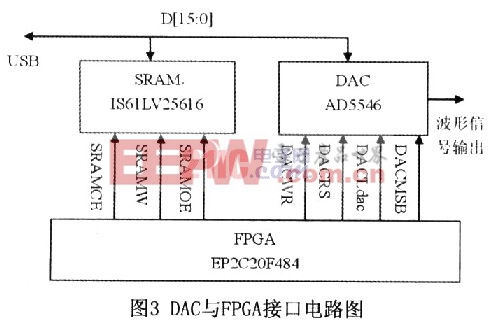

从总体工作过程分析可知,从USB接口下载的波形数据存储在SRAM中,SRAM循环输出数据到DAC芯片,根据DDS原理产生模拟波形。具体电路如图3所示。

IS6lLV25616是256k×16高速CMOS工艺3.3V单电源供电的静态随机存储器(SRAM),在FPGA控制下存储从USB下载的数据,并将数据循环输出到DAC芯片。AD9726是一款16位高性能LVDS DAC,具有出色的噪声与杂散性能以及真16位直流线性度。它采用CMOS工艺制造,并利用专有开关技术来增强动态性能。该器件具有较宽的满量程电流调节范围(2mA至20mA),能够以较低功耗水平工作。其电流输出配置简便,可以用于各种单端或差分电路拓扑结构。

评论