基于FPGA的人工神经网络系统的实现方法

图1中,黑圆表示输入为固定值1的神经元,用它与隐层神经元的连接权w011~w01n来表示隐层神经元的阈值,它与输出层神经元的连接权w02来表示输 出层神经元的阈值,w1I~w1n为输入层到隐层之间的连接权值,w21~w2n为隐层到输出层之间的连接权值。描述一个如图1所示网络的BP算法,它主 要包括2个阶段:

1)正向传播阶段 从样本集中取出一个样本(x,d),计算隐层各个节点(神经元)输出yI(i)=f(wl(i)x-w01(i))和输出层节点输出

2)反向传播阶段 按下式反向计算各层节点的局部梯度δ和权值修正量

。

。若激励函数f选用单极性Sigmoid函数,则:

式中,x是输入,d是期望输出,f为激励函数,η为学习率,δ(o)为输出层节点的梯度,δi为隐层节点i的梯度。

3 BP神经网络的VHDL设计

3.1 选择系统处理数据字长

在运算中,涉及大量乘累加操作,本应采用浮点运算,但是占用的硬件资源和速度都将会不理想;如果采用定点运算,运算中带来的“位增长”率将使每一级运算的 最大值可能会逐级加倍,因此如果不精心地规划设计,这些值就会溢出,结果会因为精度不够而无法使用。因此采用自定义的定点数进行基本的运算单元设计。本系 统采用不削弱神经网络能力的最小要求16位(1,5,lO)带符号定点数表示,最高位为符号位,低10位为小数位,其余为整数位。

例如:将1.5用16位(1,5,1O)带符号定点数可表示为:0000011000000000,将-2.3用16位(1,5,10)带符号定点数可表示为:10001 00100110011。

3.2 BP神经网络模块库的建立

根据文件复用性的要求,建立基于VHDL语言的BP神经网络元件库,根据层次设计的要求,BP神经网络结构的描述分为3层:第1层是前向 传输模块的描述,包括输入信号加权求和,权值的存储和非线性激励函数的实现;第2层是反向传输模块的描述;第3层是系统控制模块的描述。下面用VHDL语 言对这3层结构分别进行设计。

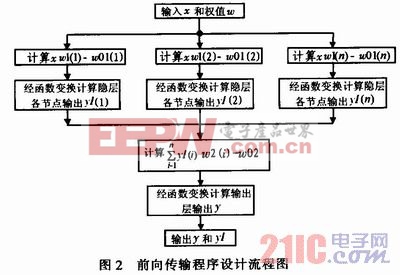

3. 2.1 前向传输模块的设计

图2为前向传输模块的VHDL程序设计流程。计算时x和w都是16位有符号数。相乘后为3l位数(最高位为符号位(两输入数符号位相异 或),低20位为小数位,其余10位为整数位),为了节省硬件资源四舍五入,舍去低10位小数位,为了防止后面相加是溢出,再扩展4位整数位,所以乘累加 后输出为25位。本文引用地址:https://www.eepw.com.cn/article/191453.htm

函数变换部分:对于FPGA硬件来说,其可实现的运算极为有限,而BP网络中的作用函数sigmoid函数是非线性的,是硬件实现的一个难点,常用的实现 方法是查表法,这种方法比较简单,但需要占用较多资源,当需要实现的网络规模较大且精度要求较高时,查表法的实现有很大障碍;还有一个方法就是多项式逼近 法。本系统使用了查表和多项式逼近2种方法。

评论