基于FPGA的CMI编码系统设计

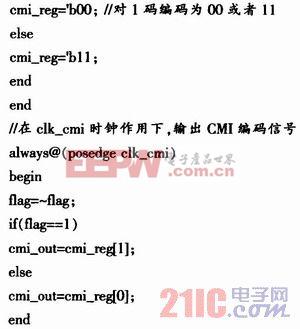

程序中主要有两个进程,其中前一个进程主要功能是在clk_m时钟作用下,产生m序列,完成CMI编码功能,由m_out输出产生的m序列,cmi_reg用于存储CMI编码值;后一个进程主要功能是在clk_cmi(是clk_m时钟速度的2倍)时钟作用下,输出CMI编码信号。

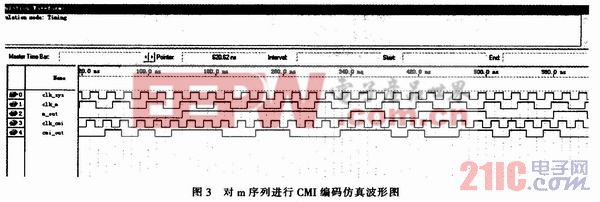

3 系统仿真结果

利用QuartusⅡ7.2软件平台对CMI编码程序进行了编译和仿真,通过仿真得到了编码仿真结果,图3给出了CMI码编码仿真波形。

从仿真结果可以看出,系统在时钟clk_m的触发下,由m_out寄存器输出m序列,输出15位的m序列值,依次为000111101011001;系统在时钟clk_cmi的触发下,完成CMI编码功能,而CMI编码后的输出值则由cmi_out寄存器输出,从仿真波形图上可以看出,CMI编码的码元输出速率是m序列码元速率的2倍。对应的输出值依次为010101110011000111010011010100,对应的CMI编码信号与m序列相比,有一定时间的延时,但编码结果完全正确。

4 结论

本文详细介绍了采用Altera公司的FPGA,利用Verilog HDL语言进行设计的CMI编码系统的具体实现方法,Altera公司的CycloneⅡ系列EP2C5Q型号FPGA具有丰富的逻辑单元,通过QuartusⅡ软件的综合仿真,可以看到程序的设计仅仅占用了11个LE,占用FPGA的LE资源还不到1%。通过以上仿真结果可以看出,编码的结果完全正确,本文阐述的设计方法是合理的。

本系统的创新点是将FPGA应用于CMI编码逻辑的开发中,使系统设计简单,配置更灵活,易于扩展,摆脱了基于专用芯片设计的限制,系统采用FPGA作为CMI编码的核心单元,应用Verilog HDL对CMI编码逻辑进行描述,利用SignalTapⅡ工具对系统逻辑进行分析,具有开发周期短、成本低、效率高、升级方便等特点,系统还研究了4级移存器周期为15的m序列发生器的设计方法,这为CMI编码器的测试提供了信源基础。存在的问题是系统在设计时未能合理的选择FPGA型号,导致FPGA资源使用不尽合理,因此,在基于FPGA的系统设计过程中,为了避免产生资源浪费,一定要在设计前通过仿真手段大致的估算出设计需要的资源数量,然后选择相应的FPGA型号;但同时也要注意FPGA的容量选择要留有一定的余量,因为在大规模设计中,还可以将本文设计的CMI编码电路与其他功能模块都集成在一块FPGA中,这一点在CMI编码作为系统设计的一部分时便显得尤为重要。

评论