基于FPGA的CMI编码系统设计

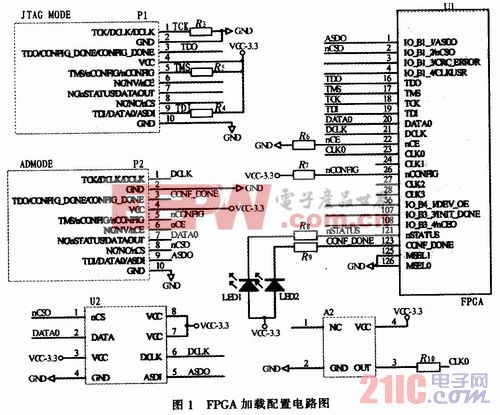

图1给出了FPGA的配置电路图,主要包括FPGA的主动(Active)方式和JTAG方式加载电路,以及专用串行配置芯片EPCS1与FPGA的连接关系。本文引用地址:https://www.eepw.com.cn/article/191302.htm

2 CMI编码系统的程序设计

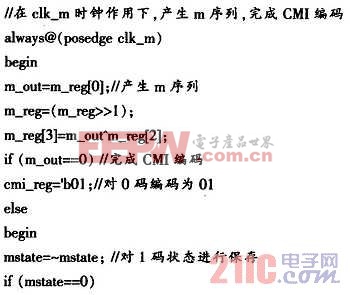

在系统程序设计过程中,将m序列作为基带输入码,然后程序再对m序列进行CMI码型变换,最后输出CMI码型。通过对CMI编码规则的分析,1位输入码元对应2位输出编码,因此CNI码元输出速率是输入m序列码元速率的2倍。在程序设计中,要保持m序列进程时钟为CMI编码进程时钟的2倍频,这是完成CMI编码任务的前提。

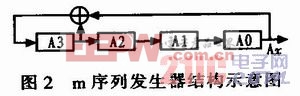

m序列是最长线性反馈移存器序列的简称,m序列具有平衡性、游程特性、线性叠加性、自相关特性和伪噪声特性,应用十分广泛。设计采用m序列产生器产生的m序列作为CMI编码的数据源,用4级移存器构成周期为P=24-1=15的m序列发生器。m序列发生器的结构图如图2所示,其中A0、A1、A2、A3分别代表一个寄存器。

在对m序列进行CMI编码的程序设计时,要注意的问题是,1码对应的输出是与前一个1码的状态有关,因此要对1码的状态进行记录,从而实现1码对应的00和11码型交替输出。

CMI编码系统设计软件环境采用的是QuartusⅡ软件平台,QuartusⅡ是一种综合开发工具,它集成了Altera的FPGA/CPLD开发流程中所涉及的所有工具和第三方软件接口。通过使用此综合开发工具,设计者可以创建、组织和管理自己的设计,主要包括设计输入、综合、布局布线、时序分析、仿真、编程与配置过程。QuartusⅡ支持多时钟定时分析,内嵌SignalTapⅡ逻辑分析器、功率估计器等高级工具,易于管脚分配和时序约束,具有强大的HDL综合能力。

SignalTapⅡ逻辑分析器是很重要的测试工具,它是对FPGA的硬件信号进行读取,可以捕获和显示FPGA内部的实时信号行为,从而能够让设计者直观的判断出逻辑是否准确。SignalTapⅡ的功能类似于逻辑分析仪,但与传统的逻辑分析仪相比,具有如下优点:使用SignalTapⅡ逻辑分析器不占用额外的I/O管脚,若使用传统的逻辑分析仪观察信号波形,则必须将待观察信号引到空闲管脚;SignalTapⅡ逻辑分析器不占用PCB上的空间,若使用传统逻辑分析仪,需要从FPGA器件上引出测试管脚到PCB上,这样增加了PCB走线难度;SignalTapⅡ逻辑分析器还不会破坏信号的完整性;SignalTapⅡ逻辑分析器集成在QuartusⅡ软件中,无需另外付费,而传统的逻辑分析仪则价格昂贵。

程序采用Verilog HDL语言进行设计,下面给出了CMI编码的部分源程序:

评论