基于FPGA和LabView的遥测信号模拟源设计

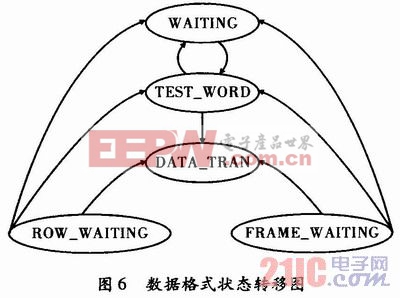

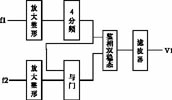

发送数据时控制单元将从单口RAM中读取的待发送数据存放在FPGA中的乒乓RAM中,并串转换后发送数据。FPGA读取外部RAM数据存入乒乓RAM的时间必须小于并串转换后发送8位数据的时间,否则会造成数据丢失。发送的数据格式通过有限状态机控制,状态转移图,如图6所示。本文引用地址:https://www.eepw.com.cn/article/191246.htm

3 结果测试

本设计FPGA芯片采用Altera公司的EP2C8Q208C8,使用QuatusⅡ8.1开发系统实现编程和仿真,完成对电路设计的功能和时序分析。

在QuatusⅡ中编译工程后,建立SignalTapⅡ文件并加入工程、配置STP文件、编译并将STP文件同原有的设计下载到FPGA中。人机交互界面设置发送频率为5 MHz,图像数据为循环发送0~127,数字量信息字为0~253,点击LVDS开始按钮。通过SignalTapⅡ窗口下查看逻辑分析仪实时捕获的数据,格式与要求完全一致,发送数据正确。实时捕获数据,如图7所示。另外,SignalTapⅡ中设置的采样时钟频率要大于被测信号最高频率的2倍,否则无法正确反映被测信号波形的变化,测试完毕后要将该逻辑分析仪从项目中删除。

4 结束语

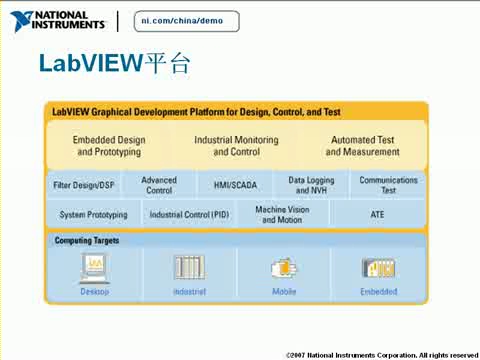

文中探讨了基于FPGA和LabView的遥测信号模拟源的设计,采用了“FPGA+接口+PC”的设计方案,实现了由PC程控、传输速率4~8MHz、固定帧格式的LVDS信号。通过此方法可以在短时间内构建一个通用灵活的虚拟仪器平台,接口可以根据实际条件采用USB、串口、红外等多种方式。

评论