基于FPGA的IEEE 1394b高速数据传输系统

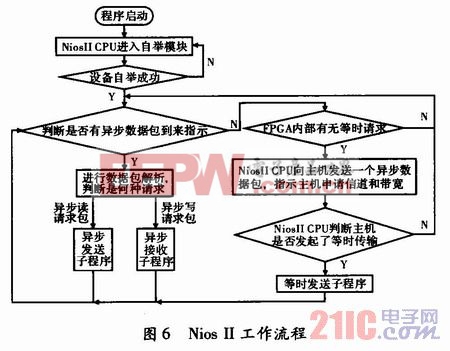

本系统中Nios II主要完成3个功能:(1)实现1394b设备的自举,协助主机完成设备识别以及设备的身份确认。(2)实现异步数据收发功能,异步读、异步写,根据请求包的类型进行分别处理。(3)满足传输条件时,为等时传输申请等时信道和带宽,成功后开始组织等时传输,传输结束后释放信道和带宽。图6为Nios II工作流程图。本文引用地址:https://www.eepw.com.cn/article/191244.htm

下面介绍等时传输过程,根据系统设计,将外部DVD压缩图像数据作为等时数据来处理。具体过程如下:

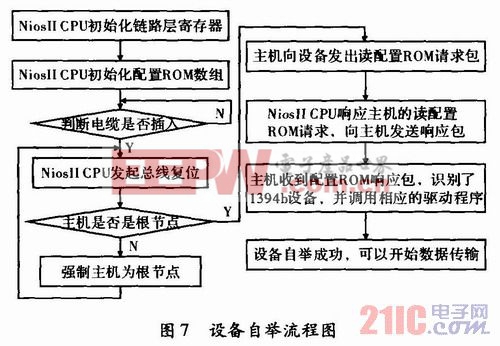

(1)NioslI CPU对1394b的OHCI和链路层寄存器进行初始化,判断线缆是否插入,强制根节点,直到设备完成自举,节点的身份确认,如图7所示。

(2)自举过程结束后,Nios II CPU检测等时传输的条件是否满足,如果满足则向主机发出申请,申请等时信道和带宽。

(3)申请成功后,Nios II CPU开始组织数据进行传输。首先它向DMA控制器发送寄存器配置信息,从而将数据传送任务交由DMA控制器完成。

(4)DMA控制器从FPGA的缓存单元中取出数据,并添加包头将数据拼接成合法的等时数据包格式,并发起PCI主模式传输。

(5)数据经由PCI总线传送到链路层芯片中,又通过物理层芯片传送到1394b总线上,并由主机上连接的数据采集卡接收,最终由主机端的应用程序解压缩和播放数据。

3 结束语

文中介绍了一种基于FPGA的IEEE 1394b高速数据传输系统,它能实现外部多路数据的实时传送。由于支持1394b的设备与支持1394a的设备可以相互兼容,所以在此基础上可以建立1394组网平台,实现多个系统的互联与传输。

评论