FPGA平台实现最小开关损耗的SVPWM算法

当-π/3≤α≤π/3,零矢量,以为中心的30°区域的零矢量为,这样三相桥臂就分别有着连续的60°的常开和常闭区域,三相桥臂的切换时间如表2所列,其中:Ta=Tx/2,Tb=Ty/2,Tc=(Tx+Ty)/2,Td=(T-(Tx+Ty))/2,Te=Td+Ta=(T-Ty)/2,Tf=Td+ Tb=(T-Tx)/2。本文引用地址:https://www.eepw.com.cn/article/191146.htm

这样就可以使得负载功率因数角为0°的三相电流波形的峰值落在桥臂没有开关动作的60°区域内,从而达到减小开关电流的目的。

3 Simulink仿真结果

根据前文所述理论,搭建Simulink仿真模型,三相逆变器的负载电阻R=5 Ω,负载电感L=0.5 mH,当逆变器的负载对称平衡时,功率因子约为0.999,此时α近似为0°,直流电压为690 V,调制比M=0.9,矢量空间被划分为12个扇区。Simulink仿真模型算法模块包括坐标变换模块、扇区判断模块、扇区时间选择模块、桥臂时间切换模块。

仿真结束后逆变器输出3相的电流波形见本刊网站www.mesnet.com.cn——编者注。三相之间电流相差120°,矢量空间被分为12个扇区,在以a相电流峰值为中心的60°区域中,调制波为1或0,即a相桥臂是没有开关动作的(常开或常闭)。仿真结果验证了前文的理论分析。

4 基于FPGA的实现及实验仿真结果

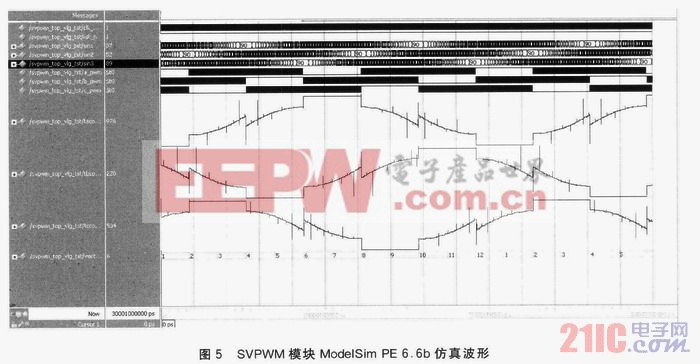

选择Altera CycloneⅡ系列EP2C8Q208为FPGA的硬件核心,实现环境是QuartusⅡ9.0,FPGA硬件描述语言采用Verilog HDL,仿真环境ModelSim PE 6.6b。如图5所示,三相调制波形相位与Simulnk仿真一致,调制波毛刺部分为FPGA内部逻辑延迟时间,小于FPGA所能识别的最小时间,对本系统的设计无影响。由图中三相桥臂的上开关的控制信号可知,桥臂在一个开关周期内有120°的区域是没有开关动作的(60°常开,60°常闭),因此系统的时序设计是正确可靠的,也验证了上述理论以及Simulink仿真的正确性。

结论

本文实现了基于FPGA硬件平台的最小开关损耗SVPWM算法。此算法相比于传统SVPWM算法,在提高开关频率的同时减少了开关损耗,可以根据实际负载的功率因子来判断零矢量的选择以及零矢量在扇区中的位置,控制桥臂开关的切换。FPGA硬件平台的实现为今后实现更复杂的控制算法奠定了基础,相比MCU/DSP,基于FPGA硬件实现的SVPWM有着更好的实时性能,其模块化的设计也有着更好的灵活性,为进一步升级控制性能提供了便利。

评论