基于FPGA的时统模块可靠性设计

3.1.1 阻抗控制

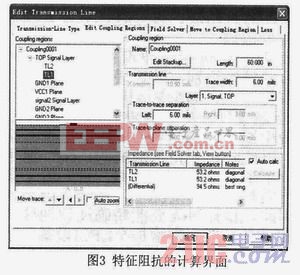

PCI Express规范对信号线的特征阻抗要求为:差分阻抗100 Ω,单端阻抗50 Ω,特征阻抗的误差范围为±10%。特征阻抗主要由线宽、线间距、铜皮厚度、介质层厚度、介质材料等因素决定。特征阻抗的计算界面如图3所示,经计算,特征阻抗为94.5Ω,满足要求。本文引用地址:https://www.eepw.com.cn/article/191093.htm

在高频电路中,损耗是一个需要重点考虑的因素。在设计中需要采取控制线长、选择介质等手段加以控制。根据在模块上可能出现的最坏情况设置参数:表层走线宽度0.1778mm,走线间距0.1524mm,走线厚度0.1016mm,走线长度为762mm的情况下得到结果如图4所示,进行仿真得到驱动端的眼图符合要求。

3.2 后仿真的实现

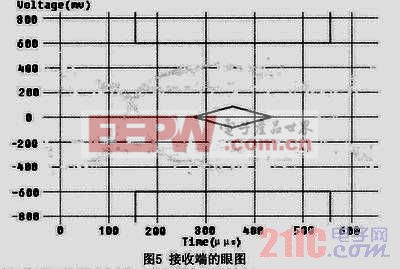

后仿真主要是在PCB绘制完成后,在前仿真的基础上将PCB相关的数据导入后再进行的仿真。在将PCB参数导入后进行仿真,结果如图5所示。信号幅度满足要求,在接收器可以识别的范围之内。

根据仿真的结果,得到如下结论:

(1)制板时,要求PCB厂家将差分阻抗控制在100 Ω;

(2)PCI Express总线要按照差分线方式走线,差分对间距保持一致;

(3)PCI Express总线差分对之间的间距保持在0.762mm以上(有空间尽量大);并且和其它类型信号线的间距尽量保持在0.762mm以上(有空间尽量大)。

(4)时钟线一定要走成差分线,保持与其它信号线间距大于0.762mm。

4 结束语

本文详细介绍了作战系统时间统一同步的可靠性设计,从EMC设计、高速电路PCB设计、FPGA逻辑编程设计等几个方面介绍了时统接收处理模块的抗干扰设计及其实现方法,并用仿真技术进行仿真,从而将时统系统可能受到的干扰减到最低,提高了整个作战系统的可靠性。文中的时统模块已经应用于实际的作战系统中,效果良好。

评论