基于FPGA的数字选频器设计

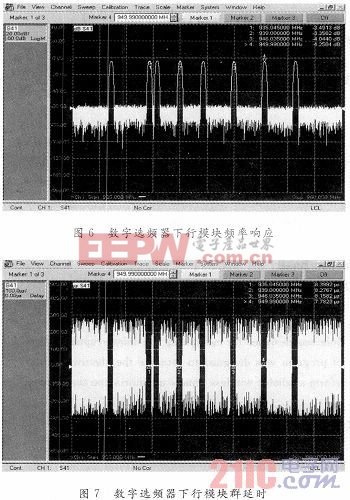

通过网络分析仪测试数字选频器下行模块的频率响应和群延时,如图6,图7所示。本文引用地址:https://www.eepw.com.cn/article/190500.htm

从图6可以看出,该数字选频器能够实现比较好的选频功能,被选出的有效相邻信道之间最小间隔能达到1 MHz;从图7可以看出该系统的群延时比较小,表明设计的滤波器性能较好,信号失真较小,系统实时性较好,能够满足实际应用的要求。

4 结语

本文介绍了应用于GSM系统商放站的基于FPGA的八通道数字选频器的没计。数字选频器应用于直放站中,能够起到降低信道之间相互干扰的作用,仪放大选中的频段信道,被选中的信道之间最小间隔能达到1 MHz,且群延时小,系统实时性好,具有较好的选频效果,能够满足实际应用要求。该数字选频器的设计采用低成本器件,小巧轻便,易安装,成本低,具有良好的市场应用前景。

评论