高性能维特比在卫星导航接收机中FPGA实现

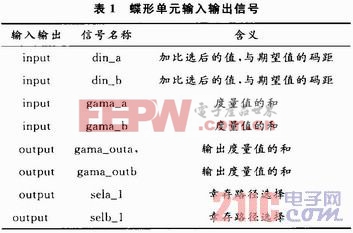

输出信号为幸存路径、度量值和,选择输出为1,不选输出为0,如表1所示。本文引用地址:https://www.eepw.com.cn/article/190478.htm

(2)幸存路径存储。经过蝶形单元运算的输出,幸存路径,64个状态,幸存路径为64位,表示该状态有或无,每进行一次蝶形运算,存入一个64位路径信息,存储器的写入控制信号和地址信息由状态控制单元发出,存储空间为120×64 b。

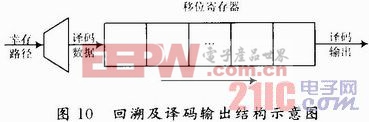

(3)回溯及输出。回溯过程即从地址最后向前一次读取幸存路径的值,得出译码电文。如图10所示。

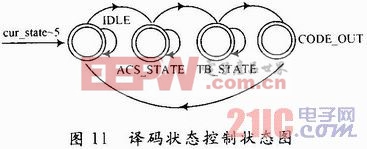

(4)状态控制单元。状态控制单元是对整个译码过程的控制,复位后,系统处在空状态,收到输入的待译数据后,进入加比选状态,按照数据流顺序进行加比选蝶形运算操作,进入到译码深度的长度的加比选后,转入译码回溯输出单元,从最后一个回溯到第一个时,即完成回溯,同时输出译码电文和译码完成中断,系统再次进入等待状态,如图11所示。

4 仿真及接收机测试结果

GPS/Galileo接收机通用的Viterbi译码器设计通过Modelsim仿真,能够得出正确译码结果,编码后在240个码序列的228之前加入1位或2位错误码,均能正确纠错,得到正确的译码结果。

译码延时260个时钟周期。最大译码数据吞吐率达240×(150×1 000 00/260)=138 Mb/s。如图12所示。

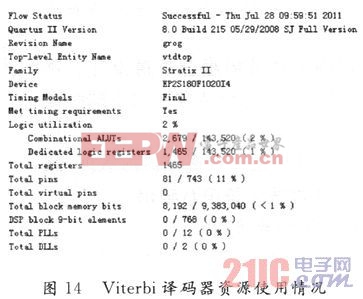

译码模块在Altera StratixⅡ系列EP2S180F1020I4 FPGA平台上,利用QuartusⅡ8.0进行综合和时序分析,最大速度可以达到150 MHz,资源使用量为:ALUTs占用2 679.Logic Registers占用1 465,与文献相比,资源消耗大大减少。如图13,图14所示。

5 结语

本文所述基于FPGA的Viterbi译码器用于GPS/GALILE-O接收机,能对GPS L2和GALILEO的电文进行译码,纠错能力达到预期效果,FPGA资源使用量较低,主时钟速度最大可达到150 MHz,译码处理延时达260个时钟周期,译码深度为120,最大译码数据吞吐率达138 Mb/s,完全满足GPS/GALILEO接收机电文接收译码速度要求。

评论