高性能维特比在卫星导航接收机中FPGA实现

2.2 加比选蝶形单元

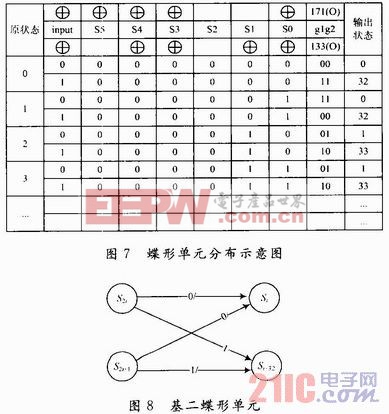

加比选(ACS)单元是完成幸存路径的延伸和判决向量的生成,计算过程包括度量值的累加、比较、选择路径操作。对(2,1,3)卷积码而言,共4个状态,组成2个蝶形运算单元;而(2,1,7)卷积码则64个状态,组成32个蝶形单元。在K=7的卷积码中,有64个状态的路径,所以根据待译码的长度,适当增加累加值的位宽,防止度量值溢出。

2.3 幸存路径存储单元

幸存路径存储是用来存储每次蝶形运算完成单元后所选择的路径,存储单元的大小为译码深度乘以状态个数。对每一个加比选过程的存储,实际就是对幸存路径的存储。

2.4 回溯单元

由VA算法可知,在网格图上经过大约5倍的约束长度之后,所有幸存路径将汇聚到一起。因此选择合适的回溯长度L,并从任一条路径开始(比如0状态)开始回溯,当回溯到L个节点时开始输出译码比特。

3 GPS L2和GALILEO E1接收机的高性能Viterbi译码具体模块设计

根据GPS和GALILEO的接口文件,L2频点电文采用(2,1,7)卷积码的形式,码多项式为(171,133)o,且与GALILEO E1的卷积码格式相同,GALILEO采用分段卷积的形式,参与卷积的为每页中不包含同步头的部分,即120位进行卷积。为了能同时作为GPS和GALILEO的译码器,设计译码深度为120的译码器。本文引用地址:https://www.eepw.com.cn/article/190478.htm

接收机的Viterbi译码模块包括:地址译码模块、数据加载模块、Viterbi译码模块、输出控制模块。为了提高译码器的性能,Viterbi译码模块的加比选蝶形单元采用32个并行结构,提高运算速度。

3.1 地址译码及数据加载

地址译码包括总线读写译码,由于Viterbi模块作为一个独立模块,内部地址采用自己的译码设计。

深度为120的Viterbi译码器,需要输入240个卷积码,对于总线32位CPU,需要8次写入完成数据输入。最少需要8个地址单元,Viterbi译码输出最少需要4个地址单元,译码状态中断输出,状态位清除,即整个译码器模块需要14个地址单元。地址线需要4根即可。

地址译码电路采用组合逻辑设计。译码状态中断输出、状态位清零采用不同时钟域同步。

数据加载模块是加载寄存器内数据,然后按照顺序,1次按2位串行输出。

3.2 Viterbi译码模块

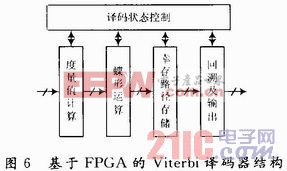

Viterbi译码模块采用的译码深度为120的(171,133)o译码设计,译码器结构如图6所示,由译码控制单元、度量值计算单元、蝶形运算、幸存路径存储、回溯输出单元构成。

(1)蝶形运算单元。按照(2,1,7),多项式为(171,133)卷积码特点,基本蝶形单元分布见图7。对于约束长度为7的卷积码,共计64个状态,形成32个基2的蝶形运算单元见图8。

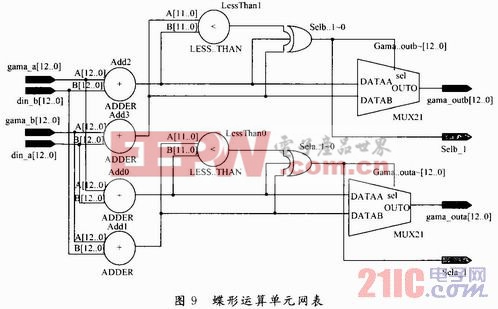

蝶形单元的输入信号为上次的度量和,与接收码本蝶形单元中理论输出码的码距度量,如图9所示。

评论