基于FPGA的MSK调制器设计与实现

经编译后生成元件,其波形仿真图如图4所示,由图可以得到:当start为低电平时,两路输出信号都为0;当start信号为高电平时,对输入信号(datain_a)有:datain_a=011111111001,此时dataout_a=010101010001,对输入信号(datain_b)有:datain_b=011110111101,此时Dataout_b=010100101001,由此可以得出,元件QDSP_PL实现了由绝对码到相对码的变换。

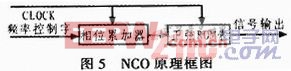

2.3 NCO的实现

2.3.1 NCO的实现原理

数控振荡器在数字中频中相对来说是比较复杂的,也是决定数字中频性能的主要因素之一,NCO的目标是产生一个理想的正弦波或余弦波,如式(8)。

式中,fL0为本地振荡频率;fs为输入信号的采样频率。正弦波样本可以用实时计算的方法产生,但这只适用于信号采样频率很低的情况。在超高速的信号采样频率的情况下,NCO实时计算的方法是不可能实现的,此时,NCO产生正弦波样本的最有效、最简便的方法就是查表法,即事先根据不同正弦波相位计算好相应的正弦值,并按相位角度作为地址存储相应的正弦值数据,工作时,在每输入一个信号采样样本时,NCO就增加一个

2.3.2 相位累加器的FPGA实现

相位累加器由N位加法器与N位寄存器级联构成。每来一个时钟fc,加法器将频率控制字K与寄存器输出的累加相位数据相加,再把相加后的结果送至寄存器的数据输入端。相位累加器输出的数据就是合成信号的相位,当相位累加器累加到最大值时会产生一次溢出,完成一个周期的动作。溢出频率就是NCO输出的信号频率。可用VHDL语言实现相位累加器的设计,其主要代码如下:

评论