基于FPGA的MSK调制器设计与实现

2 主要模块的FPGA实现

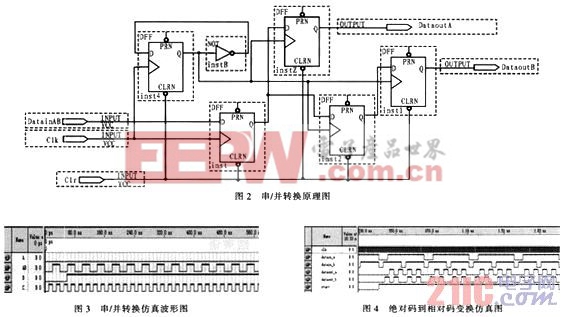

2.1 串/并转换的实现

顺序输入的二进制信息经过串/并变换器,变换成速率减半的双比特序列,可采用两个D触发器来实现,其原理如图2所示。其中DFFin st和DFFinst3构成一个两位移位寄存器,将串行输入信号变成并行输出信号:DFFinst4和NOTinst8构成二分频器,实现速率减半;DFFinst1和DFFinst2为锁存器,使信号同步输出。图3为串/并变换器S_P的仿真结果,其中AB为变换后的双比特码元。由图可以看出,当输入DataAB为01010101时,在延时约80 ns后,输出DataA为0000,DataB为1111。本文引用地址:https://www.eepw.com.cn/article/190460.htm

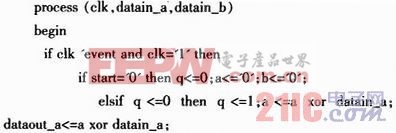

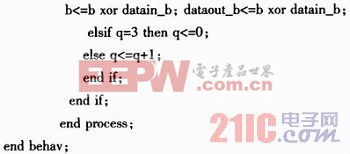

2.2 差分编码器的实现

差分编码器的功能就是实现绝对码变换为相对码,在相码中,1、0分别用相邻码元电平是否发生跳变来表示。若用相邻电平发生跳变来表示码元1,则称为传号差分码,记做NRZ码。绝对码-相对码之间的关系为:bk=ak⊕bk-1 (7)

采用VHDL设计的主体代码如下:

评论