基于FPGA的数据采集系统设计

3 系统软件设计

3.1 总体方案设计

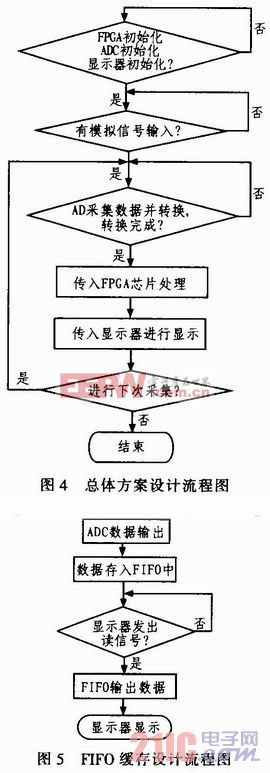

FPGA数据采集系统的软件总体方案设计流程图如图4所示。当FPGA、ADC以及12864显示器初始化完毕之后,判断是否有模拟信号输入到ADC器件中,如果没有,则等待信号的输入;如果有,则ADC开始采集数据并转换。转换完成之后,送到FPGA芯片进行数据处理。然后,传送到12864显示器中进行波形的显示。最后,再次判断有无信号输入到ADC中,如果有,则继续进行下次的采集流程;如果没有,则结束程序。

3.2 FIFO缓存设计

由于A/D转换器、FPGA以及12864显示器之间处理数据的速度不同,为了消除不必要的数据丢失与毛刺现象或者重复读取,可以将处理后的数据暂时存入FIFO中。FIFO是一个先入先出的堆栈,利用FPGA内部强大的寄存器功能,设计了一个FIFO的数据缓冲器。

如图5所示,A/D转换器将转换好的数据存入FIFO缓存中,FPGA检测显示器12864有无读信号,如果有读信号,则FIFO输出信号给显示器;如果没有,则数据继续存储在FIFO中,等待被取走。

4 结束语

基于FPGA在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。因此,本文研究并开发了一个基于FPGA的数据采集系统。本文中所提出的数据采集系统设计方案,就是利用FPGA作为整个数据采集系统的核心来对系统时序和各逻辑模块进行控制。依靠FPGA强大的功能基础,以FPGA作为桥梁合理的连接了ADC、显示器件以及其他外围电路,最终实现了课题的要求,达到了数据采集的目的。

评论