基于DSP+FPGA的高精度程控交流电源设计

摘要:介绍了一种基于DSP+FPGA芯片技术的高精度程控交流电源的实现方法,利用FPGA实现了任意波形发生功能,并对功率逆变等电路进行了详细的分析和设计,最后给出了实验结果以及相关波形。

本文引用地址:http://www.eepw.com.cn/article/190356.htm关键词:交流电源;程控;任意波形发生

1 引言

随着自动测试技术的不断发展,对程控交流电源的性能也提出了新要求,不仅要求功率大,精度高,而且要求输出范围宽,波形可任意程控。这里介绍了一种基于DSP+FPGA芯片技术的高精度程控交流电源的实现方法,利用FPGA实现了任意波形发生功能,并且获得了极高的输出精度和灵活的输出波形控制,满足各种复杂测试需求。

2 基本原理与方案

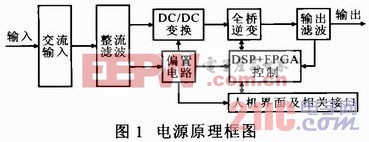

程控交流电源原理框图如图1所示。

交流输入和整流滤波电路将输入电压经过整流滤波后为后续电路提供一个较纯净的电压。偏置电路为所有电路提供偏置电压。

功率部分结构上采用两级变换,实现前后级之间隔离,主要包括DC/DC变换和全桥逆变两部分。由于输出容量S=750 VA,为减小体积、提高效率,功率变换采用开关方式。考虑到输出电压和功率的设计要求,前后级均采用全桥拓扑。前级DC/DC使用高频变压器进行输入与输出的电气隔离,同时,控制电路取样输出电压进行闭环控制,可得到稳定的直流输出。后级全桥逆变采用正弦脉宽调制(SPWM)技术,以任意波形发生器的输出为参考基准,根据等效面积原理,生成所需波形的等效PWM波。通过控制逆变电路中开关器件的通断,获得恒幅值的高频调制波形,经整形滤波后,得到需要的输出波形。利用任意波形发生器,改变调制信号的频率和幅度,可实现输出的精确调节。

DSP+FPGA控制电路是程控交流电源的核心,它实现了电源高精度实时控制和波形任意发生的需求,完成了功率电路的PID控制和与相关外围电路的通信。DSP+FPGA控制电路将输入和反馈的幅值、频率、相位等信息处理后,生成所需SPWM信号,控制电源输出,而实际输出的幅值、频率等参数在DSP+FPGA控制电路中取样标定后,送回人机界面及相关接口电路,通过液晶显示器实现信息实时显示。

3 关键电路设计

3.1 任意波形发生电路设计

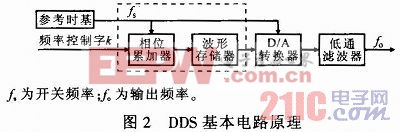

程控交流电源输出电压可编程的特性是通过参考电压信号的可编程特性来实现的。为实现电源任意波形输出,要求参考电压信号可以是正弦波(频率、幅值可根据需要设定),也可以是在正弦波上叠加谐波,还可以是任意变化的动态信号波。可见,产生高精度可编程参考电压信号的任意波形发生器的设计是程控交流电源设计中的关键环节。由于直接数字合成(DDS)技术在相对带宽、频率转换时间、高分辨率、相位连续性、正交输出以及集成化等一系列性能指标方面远超过传统频率合成技术所能达到的水平,因此采用DDS技术设计任意波形发生器,使输出具有极高的频率分辨率和快速输出转换能力,同时使用FPGA器件设计DDS电路,可以实现信号波形的多样化,而且方便可靠,简单经济,系统易于扩展。DDS的结构有很多种,其基本电路原理可用图2来表示。

波形信号的产生由高性能的TMS320C31型DSP控制器实现。该控制器具有强大的指令运算功能和数据处理能力,很容易实现各种控制算法及高速实时采样,可提高系统的工作效率。DDS电路采用FPGA设计,主要由3部分组成:①k和相位初始控制字A的接收电路,由DSP经锁存器送

到相位累加器;②相位累加器电路是整个DDS电路的核心,其精度和速度影响整个通道的性能。该电路采用VHDL语言设计。相位累加器接收DSP发送的32位k和A,在时钟脉冲的作用下,以A为起点,连续进行k值相加,生成有规律的32位相位地址码,输出锁存器将每个相位地址码锁存,取其中高18位寻址波形存储器。在相位舍位条件下,由于相位累加器的输出为周期序列,易产生有规律的杂散噪声。为此,采用抖动注入技术,用18位的随机数与要舍去的低18位相加后,再去寻址波形存储器,这样就破坏了寻址序列的周期性,将有规律杂散分量变成随机的相位噪声,从而有效消除相位舍位引起的杂散噪声;③幅度控制字U的接收、D/A转换和滤波电路。DSP将12位的U送入相应锁存器,与波形存储器中的数据一起送入D/A转换器,经低通滤波器得到所需模拟信号。

(1)频率可调设计 DDS系统采用5.5 MHz晶振,经128分频后产生42.968 75 kHz参考时钟,因此,最小频率分辨率为42.968 75 kHz/232=10μHz。若要得到45Hz~1kHz步进10μHz的频率,则k值相应取值为:45Hz时,k=45Hz/10μHz=4.5x106;1kHz时,k=1kHz/10μHz=108。因此,k值取范围为4.5×106~108。

(2)相位可调设计 相位累加器是32位的,理论上相位分辨率可达到(1/232)x360°=8.38x10-8(°)。为实现相位分辨率为0.1°,则初始相位控制字为0.1/(8.38x10-8)=1193 046。若要依次得到初始相位为0~359.9°,则初始相位值设定为1 193 046的0~3 599倍。将1 193 046以二进制形式存储于程序存储器,当接收到相位设定值时,先将设定值乘以1 193 046,再转换为相位初始控制字。

(3)幅度可调设计 在幅度调节设计中采用了双D/A的设计方法。波形D/A为DAC1,幅度D/A为DAC2,DAC1用于把波形数据转换成模拟量,DAC2用于输出信号的幅度调节。由于DAC1的参考电压由DAC2提供,因此可利用对DAC1参考电压的控制来实现幅度的调节。设计中DAC2位数N选用12位,参考电压UR取5 V。D1为DAC2的输入数据,D2为DAC1的输入数据,Uo为D/A转换器输出。由此可得:Uo=(URD1/2N)D2/2N。通过查表将数据D2读到幅度基准寄存器,可获得幅度范围0~5 V。经反馈及变换电路后幅度范围为0~300V。

评论