基于FPGA的实时数字化光纤传输系统

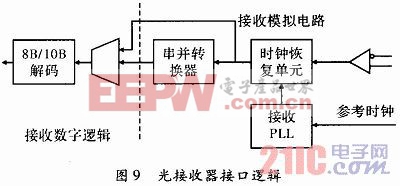

光接收器接口逻辑完成高速串行数据流到低速并行数据的转换。使用串行收发器TLK1501,其结构框图如图9所示。本文引用地址:https://www.eepw.com.cn/article/190349.htm

由专用差分端口输入的高速数据经时钟恢复单元进行时钟恢复,串并转换后进行10B/8B解码,最后传给FPGA进行解帧操作。

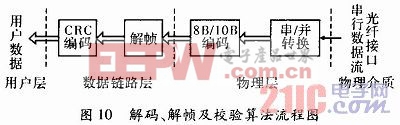

3.2.2 解码、解帧及校验逻辑

解码、解帧及校验逻辑完成数据格式转换,将接收到的数据进行10B/8B解码、解帧和CRC校验,获得有效数据。算法流程如图10所示。

4 实验仿真及波形

图11是TLK1501稳定传输数据效果。由图可以看出,TLK1501实现了实时稳定传输数据。

图12是数据收发误码测试的仿真波形图。data_all是到当前时钟为止已测试的数据总量,data_err是到当前时钟为止传输错误的数据总量,可以看出,在传输了百亿个数据后,误码仍为零。

5 结束语

研究设计了一种基于FPGA和光纤通讯的高速数字信号传输方案。实验结果表明,该方案实现了高速数字信号的实时传输,具有信号传输误码率低、系统工作性能稳定、抗干扰性强的优点,由于实际需要,系统在接收端采用TLK1501,这就限制了光纤传输的速率,若采用FPGA内部的光纤收发模块,则可进一步提高传输速率。

评论