基于FPGA的实时数字化光纤传输系统

3 软件设计

设计采用自顶向下的模块化设计方法,用Verilog硬件语言编程,实现FPGA对光纤接口处芯片、A/D和 D/A转换器等外围电路的控制。

3.1 发送端FPGA程序设计

发送端FPGA逻辑设计主要包括采样存储逻辑、校验、成帧及编码逻辑和光发送器接口逻辑。

3.1.1 采样存储逻辑

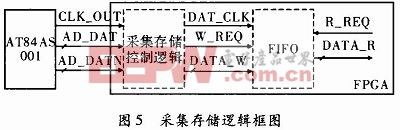

采样存储逻辑完成数据的采集以及实时存储。其逻辑形式及原理框图如图5所示。本文引用地址:https://www.eepw.com.cn/article/190349.htm

AT84AS001是ADC芯片。输入的差分数据直接接到FPGA的专用差分引脚。采集存储控制逻辑包括LVDS接收以及数据重组等模块,通过LVDS接收器将双沿时钟变为单沿,数据重组模块进行数据重新排序,还原原始数据流。最后在FIFO中进行缓存。

3.1.2 校验、成帧及编码逻辑

校验、成帧及编码逻辑完成数据格式转换,将处理后的数据进行CRC编码、成帧、8B/10B编码和并串转换。算法流程如图6所示。

3.1.3 光发送器接口逻辑

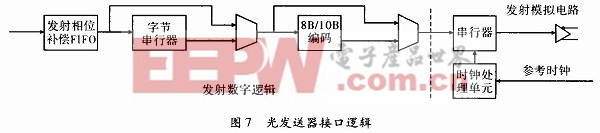

光发送器接口逻辑完成帧数据到高速串行数据流的转换。直接利用FPGA内部的专用收发器,其结构如图7所示。

帧数据首先南发射相位补偿FIFO模块进行相位补偿,抵消时钟相位差,然后通过字节串行器将数据转换为8位,接着进行8B/10B编码,并由串行器转换为高速数据流,由专用差分输出口输出。

3.2 接收端FPGA程序设计

发送端FPGA逻辑设计主要包括光接收器接口逻辑和解码、解帧及校验逻辑。

3.2.1 光接收器接口逻辑

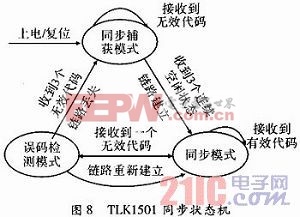

TLK1501有一个状态机,负责监测不同的工作状态,即同步捕获模式、同步模式和误码检测模式。上电或复位后,状态机进入同步捕获模式,当接收到3个连续的IDLE码或载波扩展码或1个有效数据或错误延时,即进入同步模式。在同步模式下进行数据的正常接收与发送。在这个模式下,TLK1501接收到一个无效代码,状态机立即进入误码检测模式。检测模式收到4个连续无效代码时,TLK1501立即重新进入捕获模式。TLK1501同步状态机如图8所示。

评论