基于CPLD的多DSP及FPGA远程加载设计

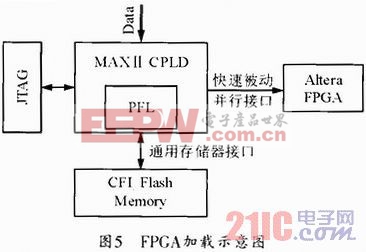

对Stratix系列的FPGA而言,加载过程相对复杂,实现起来比较困难,因为FPGA在加载过程中不仅要满足时序控制,而且加载的数据内部还含有一定的器件信息,需要满足消息格式和CRC校验才能顺利完成加载。而器件信息和CRC校验方程用户是无法得到的,因此只能采用Alte ra公司设计的MAXⅡ系列CPLD来完成加载过程。这款CPLD内部自带一个并行加载模块(PARALLEL FLASHLOADER),此模块对FPCA有专用加载接口,内部嵌入了FPGA的加载控制时序及器件信息,象一道桥梁将FPCA和通用存储器无缝连接,但硬件设计时FPGA必须设置为被动加载方式,如图5所示。系统需要对FPGA程序重构时,只需通过逻辑启动CPLD的PFL模块,PFL模块从通用存储器中读取配置数据,并且将配置数据进行格式转换打包、CRC校验后按照FPGA的加载时序写入FPGA内部,然后上拉配置完成标志位来启动新程序运行,实现FPGA的功能重构。本文引用地址:https://www.eepw.com.cn/article/190244.htm

利用MAXⅡ系列CPLD不仅可以实现单个FPGA程序的加载,也可以根据实际应用需求通过硬件扩展以及在CPLD中增加泽码控制逻辑实现多个FPCA的加载。满足系统复杂的使用要求。

3 结束语

本设计采用MAXⅡ系列CPLD作为数字处理模块的主控芯片,来实现整个模块工作状态检测、时序管理以及多个DSP芯片和FPGA芯片的程序更新升级和加载,充分利用MAXⅡ系列CLPD芯片的硬件资源、合理调用内嵌加载逻辑模块,有效规避FPGA芯片与通用Flash芯片接口不匹配带来的设计缺陷,简化了FPGA芯片程序加载复杂度。不仅可以远程控制更新重构,还可实现动态重构,这都给处理器芯片以及FPGA芯片的加载方式和应用提出了更高的要求。

本模块已经随某通信终端完成了试飞鉴定测试,模块各项指标优异、远程更新、重构功能稳定可靠,均达到了设计要求。实现了系统模块通用化,波形功能多样化,使用维护智能化的设计要求。

评论