基于CPLD的多DSP及FPGA远程加载设计

2 远程更新硬件实现

远程更新和加载就是系统具有从远端通过下发指令或参数对处理模块中存储的应用程序进行修改升级的功能,模块内部控制单元启动加载模块,完成模块功能重构。反映到硬件功能就是主控芯片要具备擦除、读写模块内存储芯片的功能,可以控制模块内的各处理器及可编程器件重新加载运行新程序。数字处理模块采用4颗DSP芯片和1颗FPGA来完成系统的数据处理任务,因此在系统升级时需要对4个处理器或部分处理器及FPCA的程序进行更新并重新加载。所以主控芯片要具备擦除、读写各DSP和FPCA芯片挂接的FLASH芯片,并能对其完成程序加载。

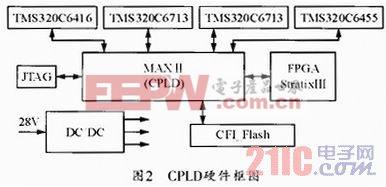

硬件设计时FLASH芯片采用了集中式设计,多个DSP芯片和FPGA分段共享同一片大容量FLASH。共享存储器有利于提高模块可靠性、模块小型化设计、有利于主控模块对其操作控制,有效降低功能实现复杂度,也有利于扩充模块功能。一般FPGA设计多采用挂接与之匹配的FLASH芯片,这些专用存储芯片不但具备专用接口与FPGA匹配,而且内部嵌入了FPCA信息,硬件设计时只需要将FPCA设计成主动加载模式即可。系统上电后FPGA将自动识别存储器并完成程序加载,整个过程不需要外部干预。但对于通用存储芯片来说FPGA是无法实现自动加载的。而且这种远程控制也是要通过外部干预来实现的,所以FPGA只能设计为被动模式,通过主控模块完成加载过程。而ALTERA公司专门研发了一款MAXⅡ系列的CPLD来实现StratixⅢ系列FPGA的加载管理CPLD硬件框图如图2所示。本文引用地址:https://www.eepw.com.cn/article/190244.htm

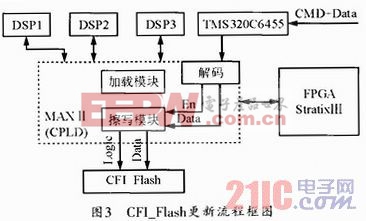

2.1 通用接口存储器(CFI Flashl更新

系统将更新数据从上位机下发至处理模块。经过CPLD解码、识别系统更新要求。CPLD将启动擦写模块,对CFI_Flash的相应空间段进行数据擦除操作,同时将更新数据写入存储器中,实现系统程序升级更新。其流程框图如图3所示。

2.2 程序重构

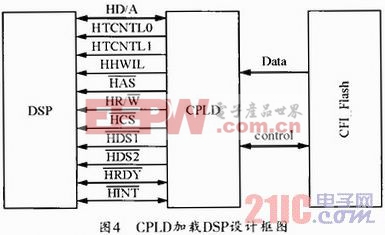

当CPLD按照系统要求将CFI Flash中程序更新完毕后,就会自动唤醒加载模块,对已更新的处理器或FPGA的程序进行重新加载。DSP的加载相对简单,将DSP设计成主机口加载模式,设计框图如图4所示。由CPLD强行复位相应DSP使其进入加载状态,然后从CFI_Flash中分别读出各DSP的目标数据,按照主机口加载时序写入DSP的内部静态存储区,加载完毕再对DSP初始化控制寄存器进行设置,完成加载过程并唤醒各DSP重新运行新程序。完成模块处理器的功能重构工作。

评论