基于FPGA的出租车计价系统设计

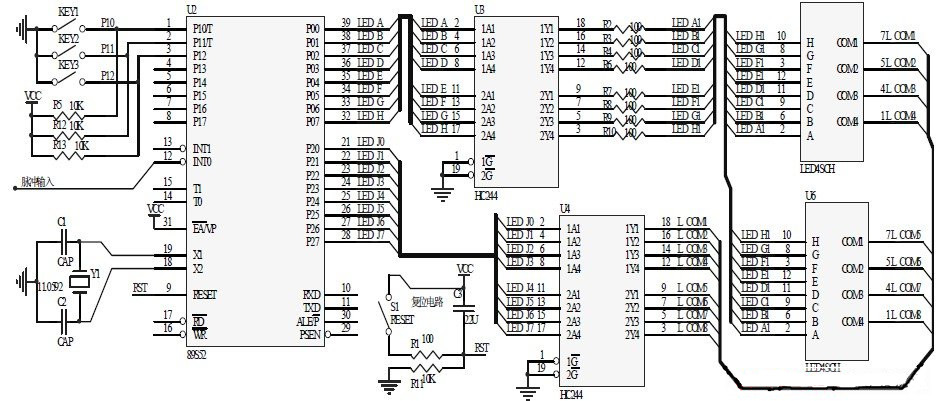

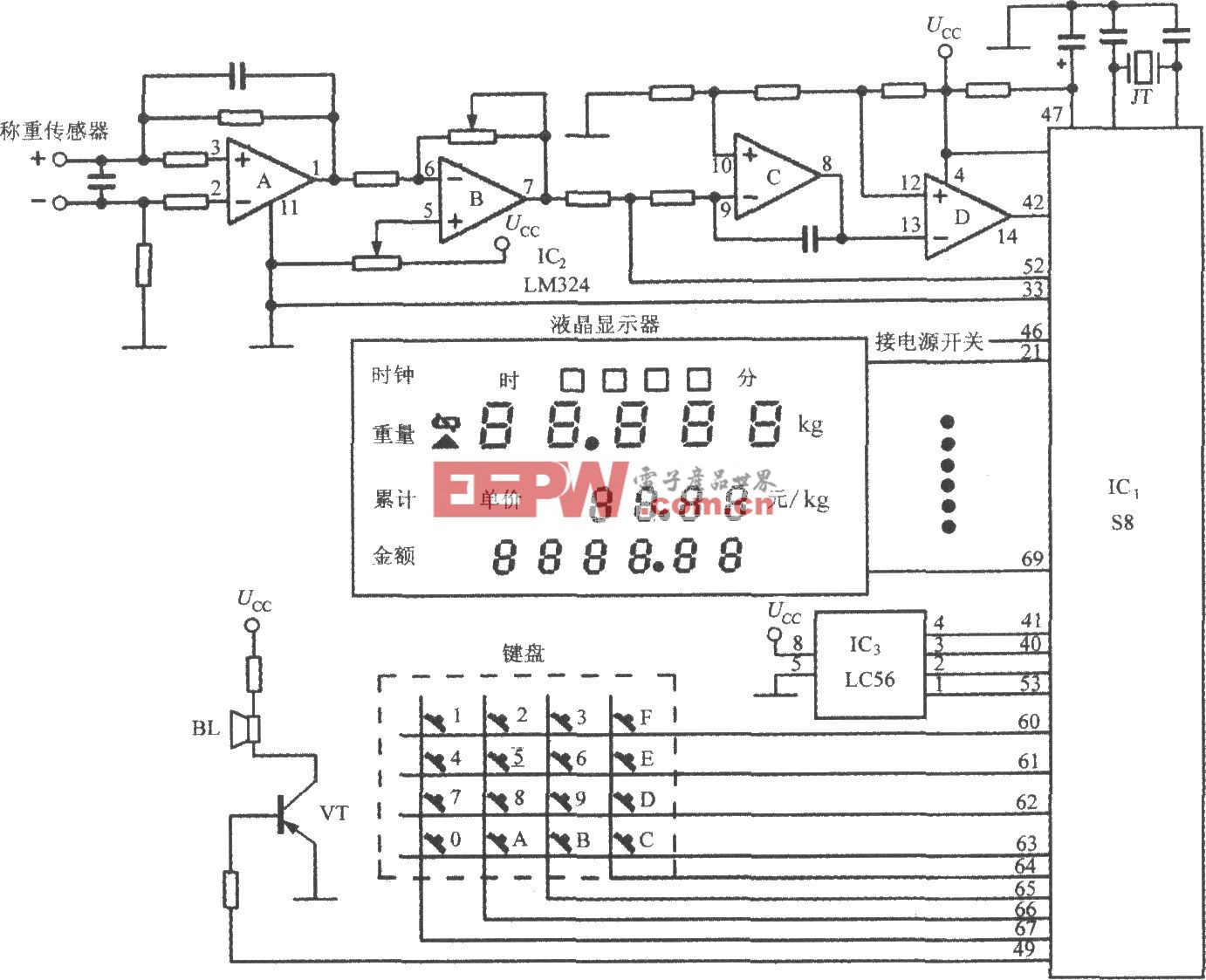

Fenpin模块是将输入端clk_240(240 Hz)的时钟信号进行分频,分别得到f_16(16 Hz),f_10(10 Hz),f_1(1 Hz)的信号,用于计量时的1.6元,1元,0.1元。

Jiliang模块用来计时和计程,fin为汽车的里程脉冲信号,当fin为高电平时,以记录的f_1的脉冲个数作为行驶的公里里程数,start是汽车计量开始信号,stop为等待信号。f_1是计量驱动信号,当f_1的脉冲到来,如果fin=1,记录f_1的个数(即行驶公里数),当行驶超过3 km,ent0输出为1。当stop为高电平时,记录f_1的脉冲个数,60个脉冲为1 min,当超过3 min时,ent1输出为1。仿真波形如图4所示。本文引用地址:https://www.eepw.com.cn/article/190206.htm

Kongzhi模块主要根据jiliang模块的en1和en0的不同输出信号选择不同的输出频率供jifei模块计费,en1=1时f=10 Hz,en0=1时f=16 Hz。

Jifei模块实际就是一个四位十进制加法器,仿真图形如图5所示,在taxi模块中,它根据不同的输入脉冲频率对脉冲个数进行计数。jil iang模块每计一次数,jifei模块就实现16次或10次脉冲计数,即实现超时时的1元/min,超里程时的1.6元/km的收费。

对整个taxi模块进行仿真,结果如图6所示,由图中可知,当stop为高电平时,汽车行驶了km1km0=35 km,计费cha3cha2cha1cha0为05 92,即59.2元,与8+(35-3)x 1.6=59.2元一致,图中当等待超过3 min时,价格按1元/min计费,仿真结果正确。

3.1.2 动态扫描显示部分

此模块包含mo8计数器、mux8_1(8选1选择器)、di_led七段数码显示译码器3个子模块。

mo8计数器:输入信号clk为系统输入的240 Hz基准时钟,输出a为模8的二进制码。

mux8_1模块是根据输入信号c[2..0]的地址码000至111分别对应了cha3,cha2,ch1,ch0,km1,km0,min1,min0八个四位BCD码,dp为小数点指示信号,在计费的第二位数字上带有小数点,仿真波形如图7所示。

评论