从StratixIII及CycloneIV开发板谈FPGA配置

最近为了给几个新同学介绍实验室所使用的两个开发板——StratixIII开发板和DEII-CycloneIV实验箱,所以整理了下关于两个板子FPGA的配置过程,从中自己也获益很多。两款芯片的配置方式算是代表了如今Altera主流的方式吧。

本文引用地址:https://www.eepw.com.cn/article/190103.htm首先介绍下CycloneIV实验箱。

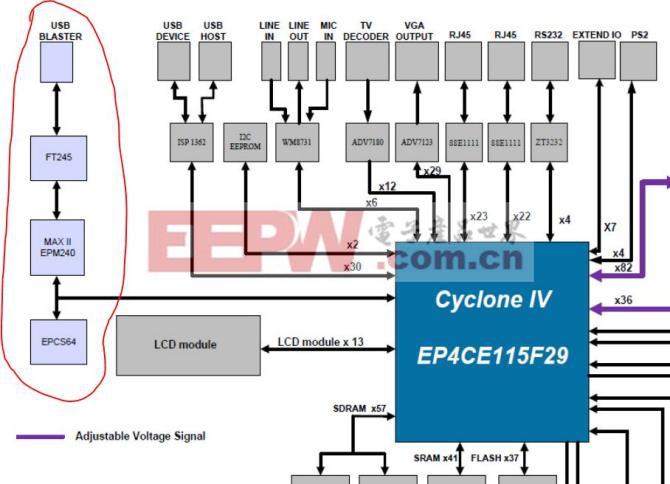

实验箱提供了简单的配置流程,首先简单介绍下CycloneIV的配置部分电路。

图中圈起部分及为FPGA配置部分电路图解,其中重点是其使用的配置芯片为EPCS64,这也是最为常用的配置方式。

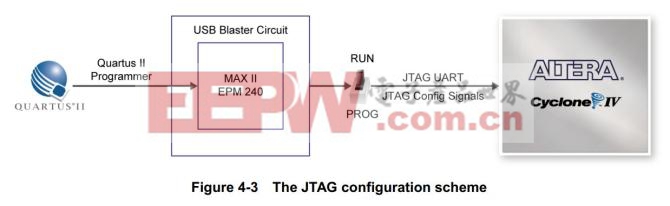

首先对FPGA可以通过USB Blaster然后以JTAG模式进行下载,如下图:

图中有个拨码开关,其中有两个可选端,一个是RUN,一个是PROG,简单的理解就是运行和程序配置。这里我比较认同RUN的含义,老师们给我们讲的时候都把将程序之间“烧”到FPGA也称作配置。但我个人觉得,运行“这个词很贴切,就好像我们是把一个文件写入到FPGA在其中运行一样。这个过程很简单,每个工程编译完成后都会生成一个sof文件,将它烧到FPGA里面就行了。

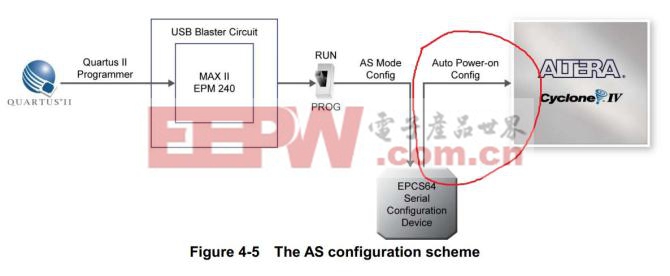

可是这样的配置每次掉电后都需要重新烧写,所以这里就需要配置芯片EPCS64来起作用了。我们把程序烧写到它里面,每次上电后,就自动由它来对FPGA进行配置,这样就不需要我们一次次的上电烧写了。

下面介绍下EPCS64的烧写了。手册中给出了它的AS模式配置:

评论