基于FPGA的可逆数制转码器设计

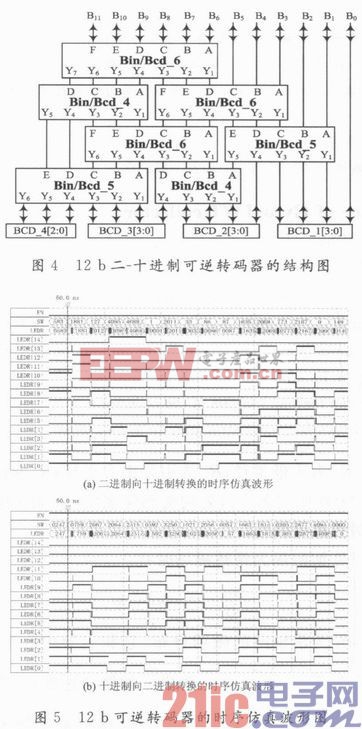

2.3 12 b可逆转码器的结构设计

根据二-十进制可逆转码算法,使用上节中得到的4 b,5 b和6 b三种二-十进制可逆转码单元模块,构造出12 b二-十进制(BCD)可逆转码器结构如图4所示,转码单元模块的多余输入端要接地,多余输出端悬利于转码器的位数扩展,也可以通过转码器的使能端BD/DB的取值分别实现从二进制到十进制和从十进制到二进制的数制转换。本文引用地址:https://www.eepw.com.cn/article/189669.htm

3 二-十进制可逆转码器的设计验证

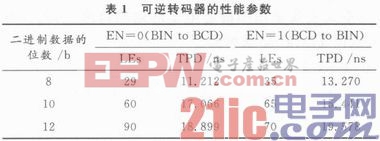

3.1 可逆转码器的时序仿真

使用QuartusⅡ9.1(Full Version)开发工具;对于图4中二-十进制(BCD)可逆转码器,在Altera公司的FPGA(EP2C35F672C6)芯片上进行了设计验证,验证结果完全达到了既定的设计目标;时序仿真结果如图5所示。在图5(a)中,使能信号EN=0,转码器实现12 b二进制数向4位十进制(BCD)数据的转换,SW是输入12 b二进制数,LEDR是输出的4位十进制(BCD)数(15 b,最大值是4 095);在图5(b)中,使能信号EN=1,转码器实现15 b十进制数(最大4 095)向12 b二进制数据的转换,SW是输入15 b十进制数(BCD),LEDR是输出的12 b的二进制数。

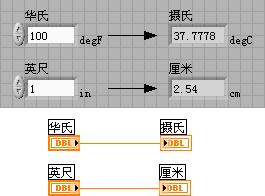

3.2 可逆转码器的性能分析

使用QuartusⅡ9.1开发工具和DE2开发板;对于所设计可逆数制转码器通过模块的参数配置,分别测试了转码器在完成8 b、10 b和12 b转码情况下的硬件实现代价(占用逻辑单元数LEs)和最大路径延迟(TPD),测试结果见表1。

表1表明,可逆转码器的数据位宽愈大转码器就越复杂,使用的单元模块就越多,实现代价增大,路径延迟也会增大,12 b可逆转码器的最高时钟频率只有50 MHz,而8 b的可逆转码器最高时钟频率可以达到75 MHz。

4 结语

文中提出以3种功能模块来构造二-十进制(BCD)可逆转码器的设计方法,通过端口参数配置和模块重构就能实现不同位数的数据在二进制和十进制(BCD)之间相互转换。从而使基于FPGA的二-十进制(BCD)转码器的构建变得简单、灵活。可逆转码器在EP2C35F672C6芯片上的验证结果也充分证明了这种设计思路的可行性;如果进一步在转码器中插入寄存器而形成流水线结构,那么转码器的运算速度就会有更大提升。

评论