基于FPGA的可逆数制转码器设计

2.2 可逆转码器的功能模块设计

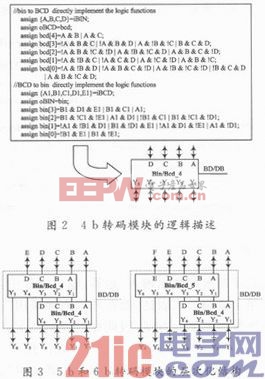

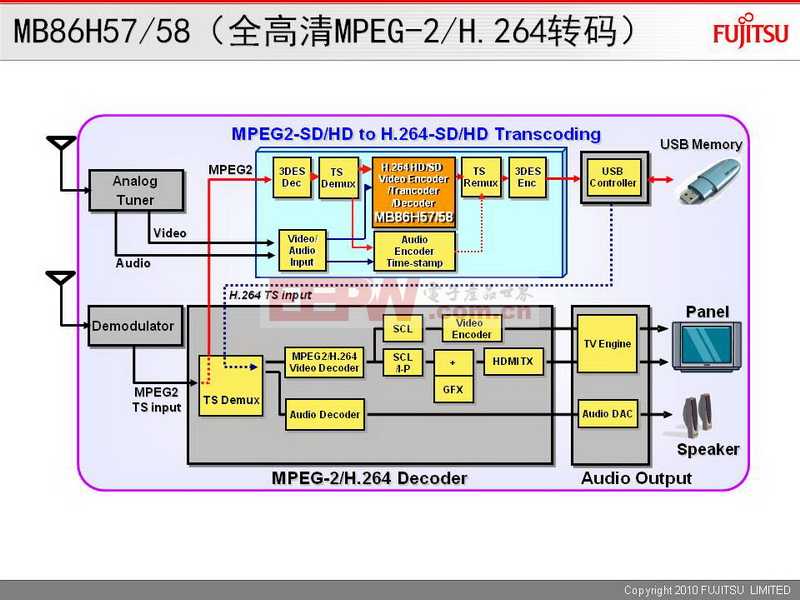

上述基于FPGA的二-十进制(BCD)可逆转码器设计方案,关键就在于要做好最底层模块(4 b转码模块)的优化设计,对4 b转码模块的不同Verilog HDL描述方式也会带来不同的实现代价;通过不同描述方式比较最终确定使用结构描述来实现4 b可逆转码模块(Bin/Bcd_4),根据参考文献[4-5,10],采用卡诺图和Multisim软件化简得到最简逻辑函数式如图2所示。再通过4 b转码模块层次实例化分别构造5 b转码模块(Bin/Bcd_5)和6 b转码模块(Bin/Bcd_6),如图3所示。本文引用地址:https://www.eepw.com.cn/article/189669.htm

评论