集成电路Cu互连线的XRD研究

2.3 Ru上Cu电镀

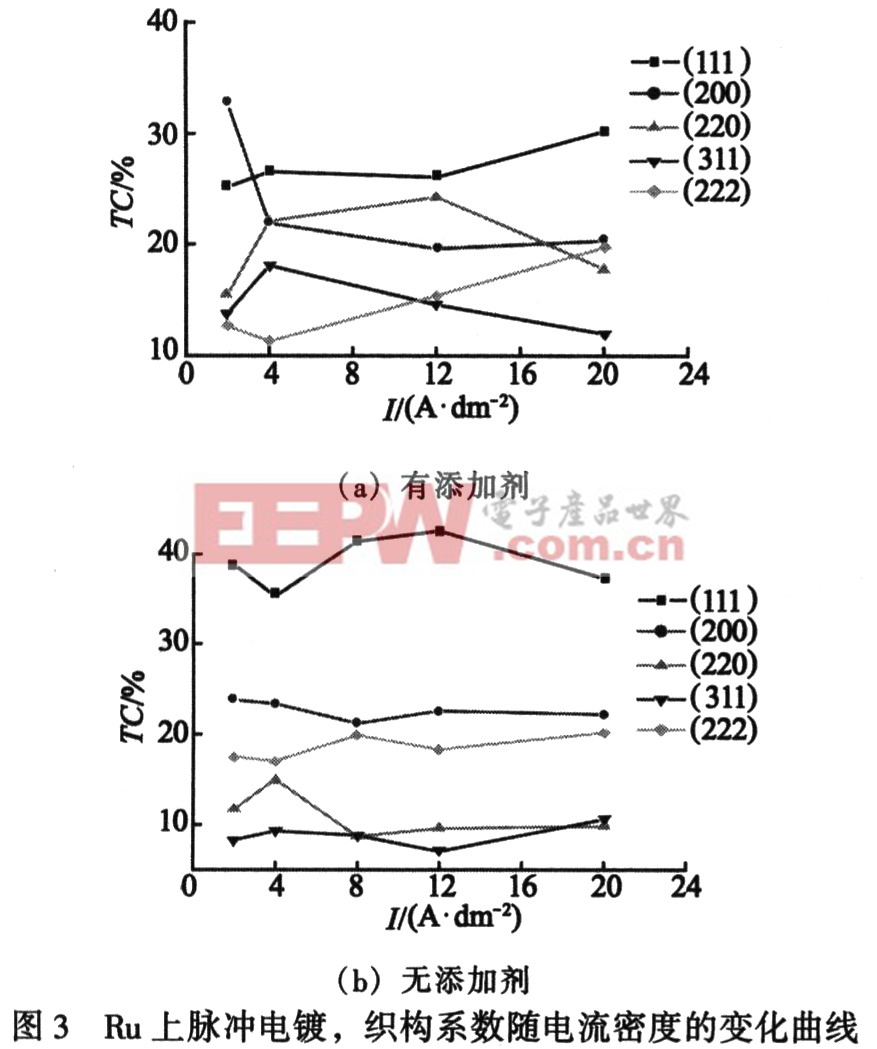

图3为在Ru衬底上脉冲电镀Cu,不同织构系数随电流密度的变化曲线。实验条件为固定ton=8 ms,toff=2ms,改变电流密度。添加剂对织构的影响情况和图l直流电镀的情况类似,添加剂对镀层织构的影响很明显,无添加剂时,(111)晶面为单一择优晶面,择优程度较高;有添加剂时,Ru上的Cu镀层在大于4 A/dm2时也呈现(111)择优。本文引用地址:https://www.eepw.com.cn/article/188973.htm

2.4 不同Cu镀层厚度的织构

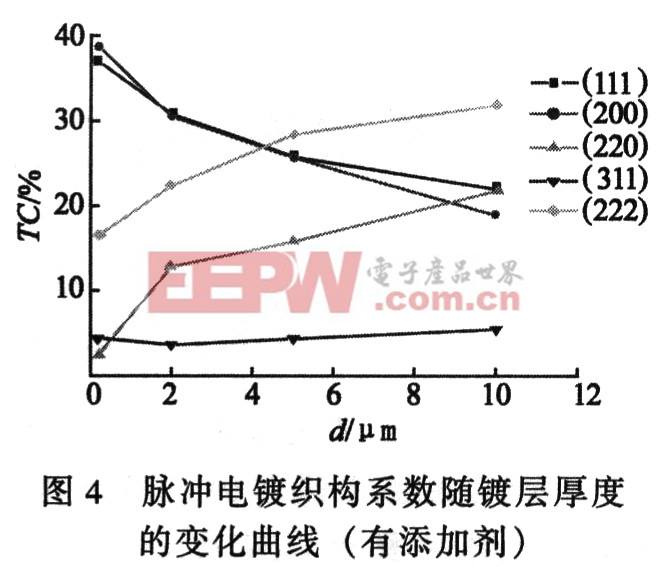

图4为有添加剂时,脉冲电镀织构系数随镀层厚度(d)的变化曲线。可见,在镀层厚度为O~10μm,随着厚度的增加, (311)几乎保持恒定,(111)和(200)晶面线性减小,而(220)和(222)晶面单调增加。当镀层厚度超过5μm时,(222)成为择优晶面。

一般认为,当Cu镀层太薄时,织构受到较强基体效应的影响,电沉积条件对晶面的影响很小,因此籽晶层的晶面在很大程度上决定了镀层的晶面情况。当Cu镀层超过4μm后,就基本不受基体外延的影响,主要由电沉积条件决定,形成绝对优势的择优晶面取向。

3 结论

Cu互连是目前深亚微米集成电路的主流技术。Cu镀层的织构和择优取向与电沉积条件、添加剂、镀层厚度以及衬底等因素密切相关。通过硫酸盐体系电镀获得的Cu镀层,本文用XRD研究了不同条件对Cu镀层性能的影响,以及不同厚度Cu镀层的织构情况。实验结果表明,对于在各种条件下获得的1 μm Cu镀层,均呈现(111)晶面择优,这样的镀层在集成电路Cu互连线中有较好的抗电迁移性能。

评论