基于FPGA的8段数码管动态显示IP核设计

4 基于Nios II的软件驱动程序设计

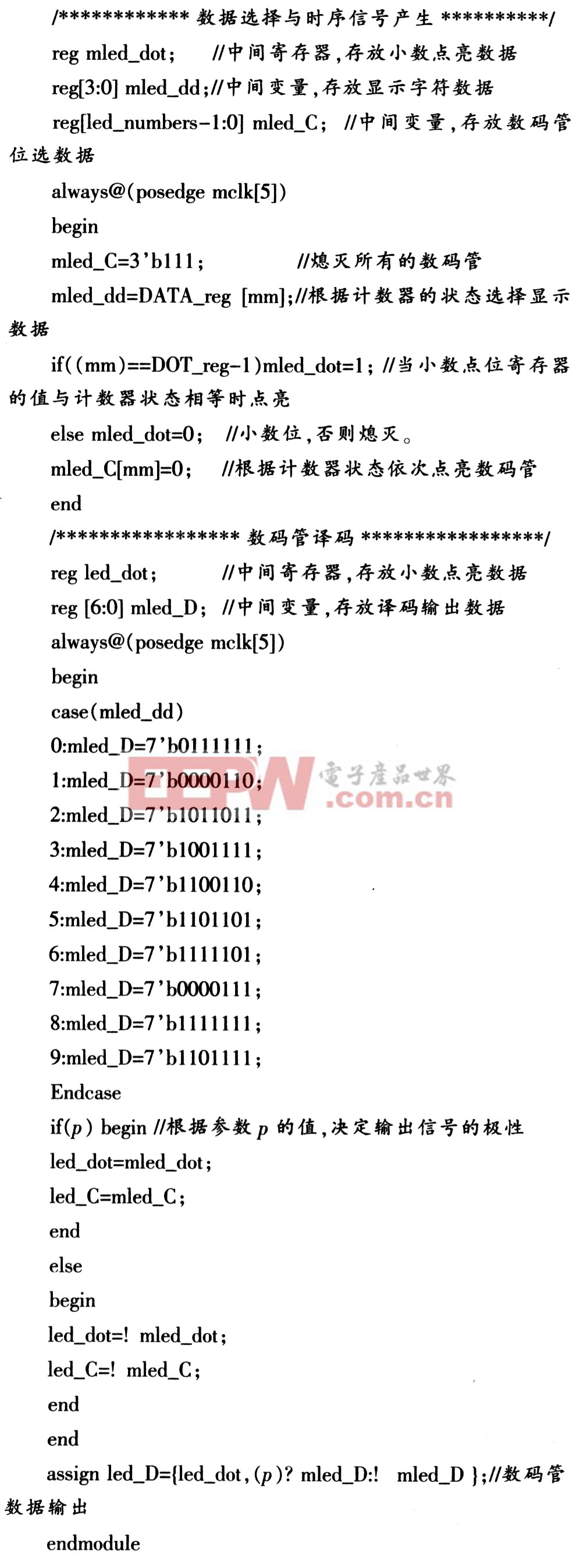

把所设计的IP核加载到嵌入式系统,打开Nios II EDS,在Ahera提供的集成开发环境(IDE)中,为IP核编写驱动程序。

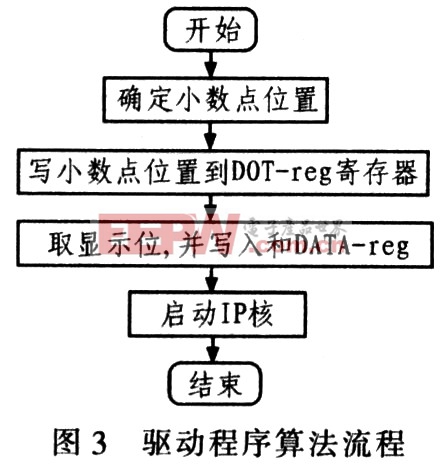

首先点击new菜单建立工程应用文件,然后选择一个空的工程模板(Blank Project),并在此工程模板中编写相应程序,其驱动程序的算法流程如图3所示。

5 结论

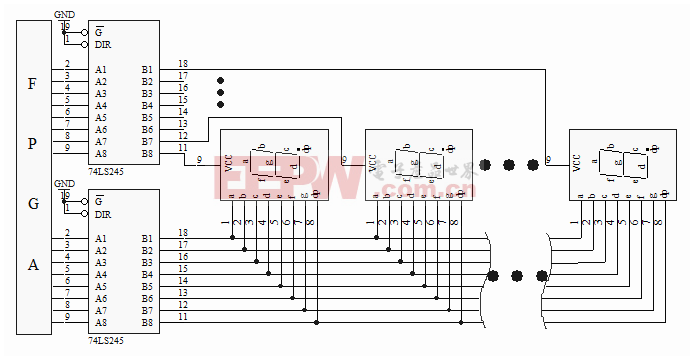

数码管是电子设计中应用较多的元器件。用于显示系统的运行状态和简单的字符,以便提升系统人机界面的效果。为减轻设计者的工作量,实现软核重用,设计8段数码管动态显示IP核,并给出此核的一个参考驱动显示程序。此核根据设计需要,可例化1~8个共阳极(或共阴极)数码管控制器,成功控制1~8个数码管工作,大大提高设计效率。测试结果表明,此核工作可靠、稳定,可直接应用于工程实践中。

评论