32阶FIR滤波器的FPGA实现

随着软件无线电的发展。对于滤波器的处理速度要求越来越高。传统的FIR滤波器一般采用通用DSP处理器,但是DSP处理器采用的是串行运算,而FPGA是现场可编程阵列,可以实现专用集成电路,另外还可以采用纯并行结构及考虑流水线结构,因此在处理速度上可以明显高于DSP处理器。本文采用并行分布式算法在FPGA上设计并实现了高速处理的32阶FIR低通滤波器,在此过程中利用Matlab的数值计算与分析功能来提高设计效率。

1 FlR低通滤波器的窗函数实现

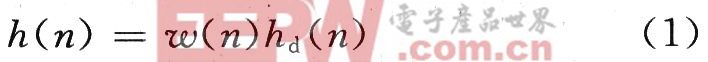

理想的滤波器频率响应中傅里叶反变换ha(n)一定是无限长的序列,而且是非因果的,而实际要设计的滤波器h(n)是有限长的,因此要用有限长来逼近无限长的,其方法就是用一个有限长度的窗口函数序列ω(n)来截取,即:

常见的窗函数有矩形窗、巴特利特窗、汉宁窗、哈明窗、布莱克曼窗、凯泽窗。其中,凯泽窗提供了可变的过渡带宽。本文采用凯泽窗对FIR滤波器进行设计,其窗函数表达式为:

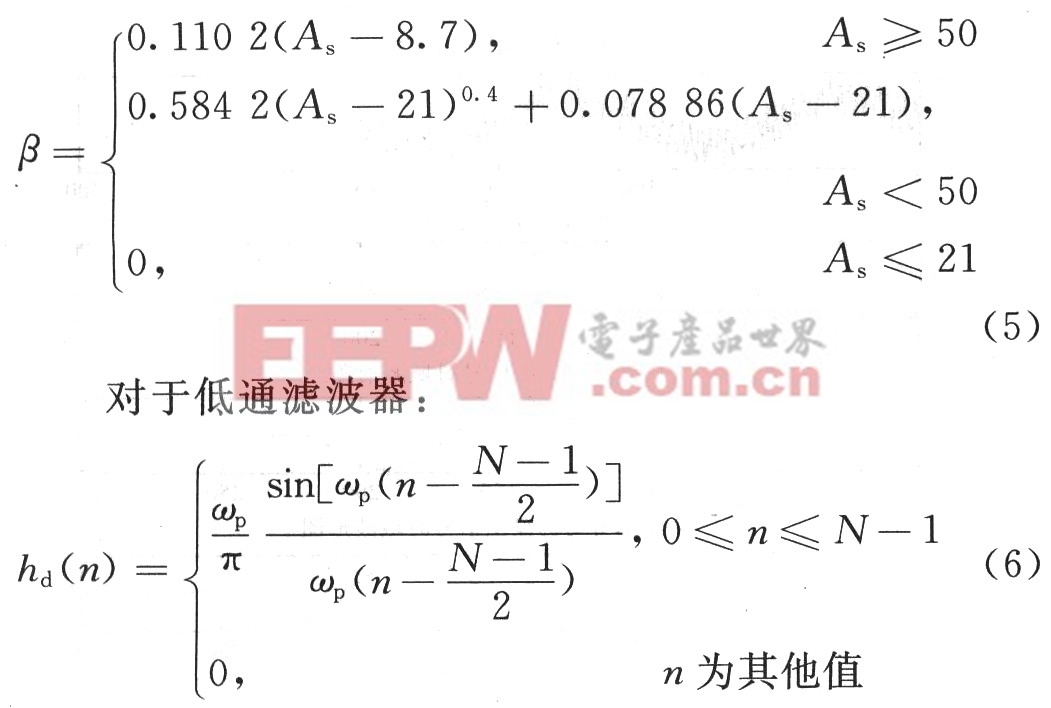

I0[・]为第一类变形零阶贝赛尔函数,形状参数β为依赖于滤波器阶数M的参数,用来调整主瓣宽度与旁瓣衰减,选择M可产生各种过渡带宽和接近最优的阻带衰减。给定通带截止频率ωp,阻带起始频率ωs,阻带衰减As,凯泽窗设计中有经典公式可供使用,如下:

过渡带宽:

![]()

滤波器阶数:

形状参数:

假设低通数字滤波器设计指标如下:

评论