基于单片机和FPGA的扫频仪设计

若选取晶振频率为40 MHz,频率控制字为24位,相位累加器的位数为31位,则输出频率范围为0.02 Hz~312 kHz,步进频率为40 MHz/231≈0.02 Hz。

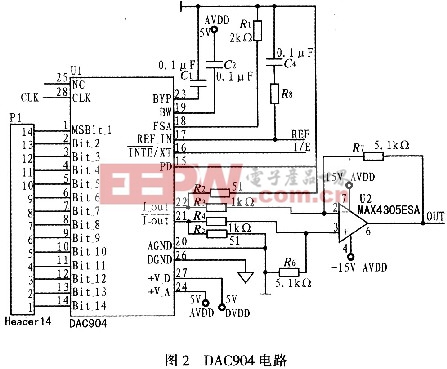

系统采用高速14-bit电流输出型D/A转换器DAC904制作DDS扫频信号源。通过FPGA给其20 MHz的时钟信号以输出10 Hz~100 kHz的扫频信号。该器件制作成的PCB板中,很好地考虑了接地,使得输出信号在频率为1 MHz可以达到无明显失真。DAC904采用内部基准和双极性接法,输出信号幅值范围为0~5 V。其原理图如图2所示。本文引用地址:https://www.eepw.com.cn/article/173225.htm

2.2 幅频特性测试方案

使用集成真有效值转换器AD637先检测出信号每个频率点的有效值,再经过A/D采样将得到的数据读到单片机中进行处理即可。该器件外接电路简单,工作频带很宽,与A/D转换器级联,可以对任何复杂波形的有效值、平均值、均方值、绝对值进行采样,测量误差小于±(0.2%读数+0.5 mV),可以达到很高的测量精度。

2.3 相频特性测试方案

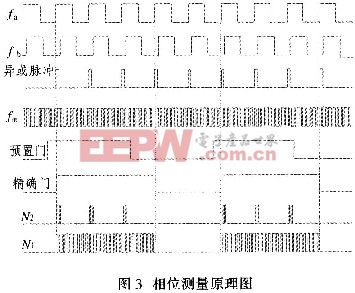

采用计数法实现相位的测量。计数法的思想是将相位量转化为数字脉冲量,然后对数字脉冲进行测量而得到相位差。对转换后的数字脉冲量进行异或运算,产生脉宽为T0、周期为T的另一路方波,若高频计数时钟脉冲周期为TCP,则在一个周期T的时间内的计数数值为:

![]()

式中,φx为相位差的度数。

这种方法应用比较广泛,精度较高,电路形式简单,适合FPGA实现。

实际测量中,当两输入信号频率较高且相位差很小时,得到的脉冲很窄,这会造成较大误差。为了克服上述缺陷,引入等精度测量的思想(如图3),采用多周期同步计数法,利用触发器产生一个宽度为被测信号fa整数倍的闸门信号。利用计数器1测量出闸门信号内通过高频脉冲fm的个数N1,利用计数器2测量出相同时间内闸门信号、异或信号、高频脉冲三者相与后的脉冲数N2。因此,相位差值为△φ=N2/N1x36 0°。测量相位的同时,在FPGA内部引入一D触发器,用一路方波信号控制另一路方波,通过触发器输出的高低以判断信号相位差范围是大于180°还是小于180°。

评论