可适应多种时序情况的DMA控制器设计

2.2.2 multiple block read

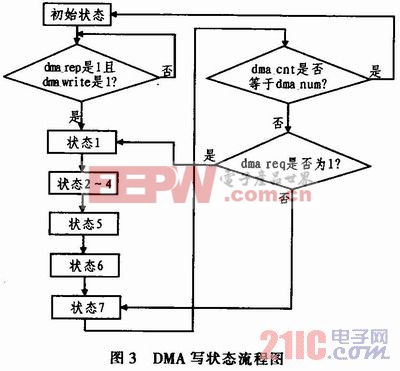

在该图像协处理器中每次multiple block read要从卡读出10个block数据并将其全部写入DMA存储器当中。当处于初始状态(状态0)的DMA状态机发现dma_req为1且dma_write信号为1时,即明确SD卡控制器将开始DMA写操作,其将依次进入状态1、状态2、状态3、状态4。在状态1中,DMA状态机会向SD卡控制器发出dma_ack信号,由于存储器读存在延时,SD卡控制器将在此后的第二个时钟上升沿(即DMA状态机在状态3时)送出dma_wdata。DMA控制器将dma_wdata暂存一个时钟周期后,会在状态4和状态5中把此32位数据依次写入DMA存储器,dma_memory_addr也将在这两个状态分别加1。在状态7中,DMA控制器也将做2个判断,首先会判断dma_cnt和dma_num是否相等,若相等说明本次multipleblock read的全部5 120字节数据已经写入DMA存储器中,DMA状态机将回到状态0等待下一次DMA操作指令;若不相等,则判断dma_req是否为1,如果为1则意味着继续做本次DMA写操作,DMA状态机也将回到状态1,开始下一个32位数据的写入;如果dma_req为0则说明SD卡控制器读卡的速度较慢,暂时还没有新的32位数据要写入,DMA状态机也将在状态7处于等待状态,直至dma_req再次为1,状态机才回到状态1,开始写入下一个32位的数据。最后当DMA控制器在状态7时发现dma_cnt和dma_num相等,意味这本次DMA操作已经完成,SD卡控制器也将向基带芯片发出中断信号,基带芯片响应该中断后将从DMA存储器中读取此5 120字节数据。其写状态流程图如图3所示。本文引用地址:https://www.eepw.com.cn/article/162296.htm

3 仿真结果

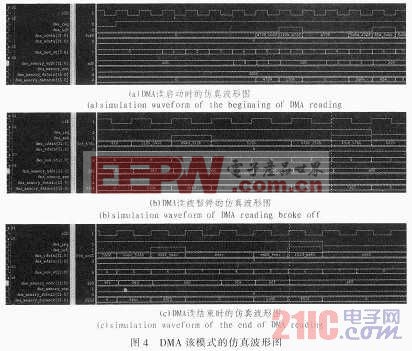

该DMA控制器的核心即为文章第2部分中所述的DMA状态机,现将multiple block read和multiple block write的几个关键时序情况的仿真波形显示如下,dma_now_st则为DMA状态机的状态变量。

图4(a)所示为一次DMA读刚刚开始时,DMA状态机翻转情况。在dma_req为1后,状态机dma_now_st则依次进入各个状态。在dma_now_st为状态4时,读出了DMA存储器的地址0中的数据16'h4739,在dma_now-st为状态5时,读出了DMA存储器的地址1中的数据16'hlf0b,之后在dma_now_st为状态6时,此32位数据在dma_rdata端口被送出;

图4(b)所示的是在一次DMA读中,SD卡控制器写卡速度较慢,其暂停DMA读操作的情况。在DMA控制器送出地址12'h394和12'h395中的数据后,SD卡控制器发现DMA读的速度较快,有可能覆盖还未写入卡的数据,所以把dma_req拉低,暂停DMA读;

图4(c)所示的是一次DMA读的结尾,此时DMA存储器已经读完了地址0~12'h9ff中的所有5 120个字节的数据,dma_now_st在状态7中监测到dma_cnt已经等于dma_num,所以状态机回到初始状态0。

图5(a)所示为在一次DMA写刚刚开始时,DMA状态机dma_now_st的工作情况。从图上可清楚看到当dma_now_st处于状态4和状态5时,DMA控制器将dma_wdata端口数据写入DMA存储器的地址0和地址1中。

图5(b)所示为在做DMA写时,SD卡控制器读卡速度较慢的情况。当SD卡控制器在dma_now_st为状态1时送出32位数据32'hb944da21后,其发现已不能在DMA状态机的下一个状态1时送出新的32位数据,所以SD卡控制器将dma_req拉低。

图5(c)所示为一次DMA写的结尾,SD卡控制器送出最后一个32位数据32'hf83dea95后,已经读出了所有5 120字节的数据,所以将dma_req拉低。dma_now-st也在向DMA存储器的地址12'h9fe和12'h9ff写完最后两个16位数据后,回到初始状态状态0,至此一次CMD18命令操作完成。

4 结束语

随着消费者对视觉效果的要求越来越高,也必然要求各种移动终端设备的图像系统功能越来越丰富,性能越来越高,因此图像协处理器的设计也变得更加重要。在此背景下,处于基带芯片和SD卡控制器之间的DMA控制器部分将面临更复杂的工作环境和更高的性能要求。这里所述的DMA状态机能够灵活适应基带芯片操作可能被打断、基带芯片写DMA存储器可能与DMA读相冲突等多种信号时序情况,起到了很好的协调基带芯片和SD卡控制器速度的作用,并使基带芯片和SD卡控制器能够尽量并行工作,使操作SD卡的速度达到210 kB/s,在实际工作中取得了很好的效果。

评论