可适应多种时序情况的DMA控制器设计

2 DMA控制器的实现

2.1 DMA控制器接口

为了更准确地描述该DMA控制器的工作流程,其主要接口信号介绍如下。DMA控制器与3部分逻辑的接口为:基带芯片的EMI接口、DMA存储器接口、SD卡控制器。

1)与基带芯片的接口 这个接口中,与该DMA控制器关系最密切的信号是host_dma_wr,其为基带芯片送给DMA存储器的写信号,这个信号低电平有效。

2)DMA存储器接口 dma_memory_addr为DMA存储器的地址信号。为了能够保存10个block的数据,DMA存储器的容量为2560x16=5120字节,所以dma_memory_addr的位宽为12位;drag_memory_datain为DMA存储器的数据输入端口,位宽为16位;dma_memory_dataout为DMA存储器的数据输出端口,位宽为16位;dma_memory_wen为DMA存储器的写使能信号,低电平有效。

3)SD卡控制器接口 dma_req是SD卡控制器发出的DMA请求信号,高电平有效。其为DMA控制器做速度协调的重要信号,如果其为高则表示SD卡控制器要求与DMA存储器做DMA传送;如果该信号被置低,可能存在两种情况,①可能是本次DMA传送已经完成,②可能是SD卡控制器的读或写卡速度低于其操作DMA存储器的速度,所以SD卡控制器暂停DMA操作;dma_write是SD卡控制器发出的DMA写标志信号。如果其为1表示SD卡控制器在做读卡操作,并准备将读出的数据写入DMA存储器;如果其为0表示SD卡控制器在做写卡操作,并准备从DMA存储器中读取数据;dma_ ack是DMA控制器发给SD卡控制器的应答信号,其相当于DMA传输数据的有效信号;dma_rdata是DMA读模式的数据输出端口,位宽为32位;dma_ wdata是DMA写模式的数据输入端口,位宽为32位。

2.2 DMA控制器的工作流程

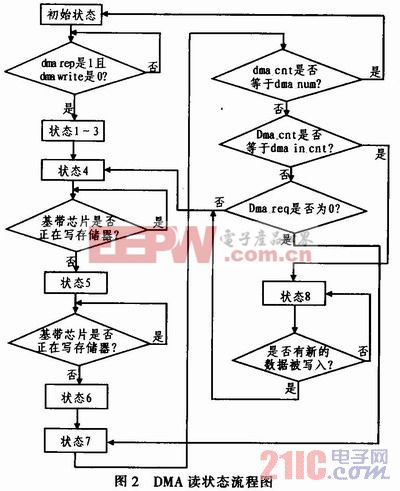

为了使DMA控制器能更灵活地适应各种操作情况并很好的完成2个操作源(基带芯片、SD卡控制器)的速度匹配功能。下面将分别就multi-ple block write命令(CMD25)和multiple block read命令(CMD18)对该状态机的工作流程进行说明。

先将状态机中的几个重要变量做如下说明:

dma_num表示在一次多block读(CMD18)或写(CMD25)操作中,要向卡写入或读出多少个字节的数据。在该图像协处理器中,每次读或写卡都要操作10个block数据,所以dma_num将被设置为5 120;

dma_in_cnt表示在一次多block写卡操作中,基带芯片已经向DMA存储器中写入了多少个字节的数据;

dam_cnt表示在本次多block操作中,SD卡控制器从DMA存储器中读出数据的字节数(DMA读模式)或写入DMA存储器中的数据字节数(DMA写模式)。

显然,在该图像协处理器中,每个CMD18和CMD25完成之后,dam_in_cnt和dma_cnt都将与dma_num相等,且均为5 120。

2.2.1 multiple block write

如前所述,每次multiple block write要向卡写入10个block数据,即10x512=5 120字节。为了提高写卡速度,基带芯片首先向DMA存储器中写入1个block数据,然后向SD卡发出CMD25(multi block write command)。当SD卡控制器发出CMD25并接收到该命令的应答信号后,立即向DMA控制器发出dma_req信号,准备从DMA存储器中读取数据。当DMA控制器监测到dma_req为1且dma_write为0后,将依次进入状态1、状态2、状态3、状态4。在状态4中,其会检查基带芯片的写信号host_dma_wr是否有效,如无效,其将从DMA存储器中读取当前地址的数据,然后再将DMA存储器的地址加1并进入状态5;如host_dma_wr有效,则DMA控制器将等待一个时钟周期,在下个时钟的上升沿再去判断host_dma_wr的极性,若其失效再读DMA存储器。也就是说基带芯片对DMA存储器的操作有更高优先级,利用这个办法就可以使基带芯片和SD卡控制器可以尽量并行工作以加快写卡速度。在状态5中,DMA读状态机做如状态4的操作,这是因为dma_rdata的数据线宽度为32位,而dma_memory_data-out的数据线宽度是16位,所以必须要读2次DMA存储器再做一次DMA读传送。在状态6中,DMA状态机将向SD卡控制器发出dma_ack(数据使能信号)和dma-rdata[31:0],随后进入状态7。在状态7中,DMA状态机将做3个重要判断,首先其判断dma-cnt是否等于dma_num,如相等则意味着SD卡控制器在本次多block操作中已经读取了全部5 120个字节数据,状态机将回到初始状态以准备下一次DMA操作;若不相等,则判断dma_c-nt是否等于dma_in_cnt,若dma_cnt等于dma_in_cnt,则意味着基带芯片写入DMA存储器的所有数据均已被SD卡控制器读出,DMA存储器已经为空,但数据量还没有达到5 120字节,DMA状态机将进入状态8即等待状态,只有基带芯片写入新的数据后,SD卡控制器才能回到状态4继续读取数据,这个分支主要是应用于SD卡控制器写卡速度快于基带芯片写DMA存储器的情况;若dma_cnt不等于dma_in_cnt,则DMA状态机将检查dma_req信号的极性,如其为1,状态机将转至状态4读取下一个32位数据,如为0则意味着此时SD卡控制器写卡的速度要慢于DMA读数据的速度,其前面通过DMA接口读出的数据还没有完全写入SD卡,所以SD卡控制器将暂停从DMA存储器中读取数据,DMA控制器的状态机也将在状态7处于等待状态,等待dma_req重新为1。当dma_req再次为1后,状态机将回到状态4开始新的32位数据的DMA读操作。最后,当第5 119和5 120个字节被从DMA存储器读出后,DMA状态机将在状态7中检查到dma_cnt=dma_num,标志至此,DMA状态机完成了一次DMA读操作的全过程。SD卡控制器将向基带芯片发出中断信号,基带芯片响应该中断后将启动下一个读卡或写卡的命令。其读状态流程图如图2所示。本文引用地址:https://www.eepw.com.cn/article/162296.htm

评论