基于FPGA的数字下变频的研究与实现

(1)由于系数的对称性,可将有相同滤波系数的输入数据先进行相加,只用其中4个系数,简化结构,节约资源。输人数据为12 b,相加后位宽扩展一位为13 b。

(2)采用全并行的DA结构,每一位数据都有一个深度为24的查找表,将数据每3位分为一组,最后一组为4位,每组查表结果移位相对应位数后相加,结果输入两级流水线加法器阵,最后得到滤波输出值。

(3)设计中应注意的三个问题:

①滤波器系数的量化,把系数扩大2L倍,最后输出右移L位即可。

②查找表的建立。由于只有4个系数,不用对系数进行分组分别查表以节省查找表资源。

③运算中数据位数的处理,不要溢出。

第二级滤波器的实现跟第一级滤波器类似。本文引用地址:https://www.eepw.com.cn/article/158029.htm

4 仿真及结果分析

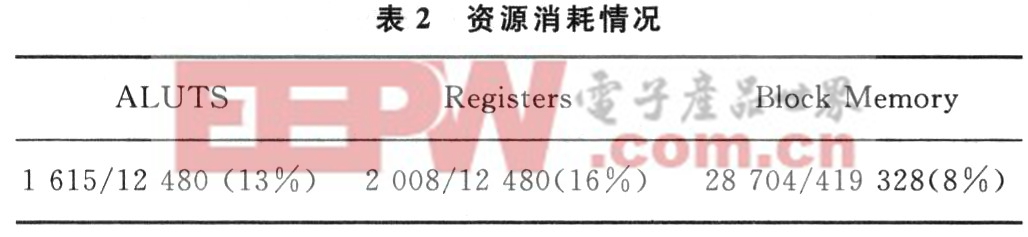

FPGA芯片采用Altera公司的StratixⅡEP2S15F484C3,在QuartusⅡ7.2中布局布线后,资源消耗情况如表2所示。

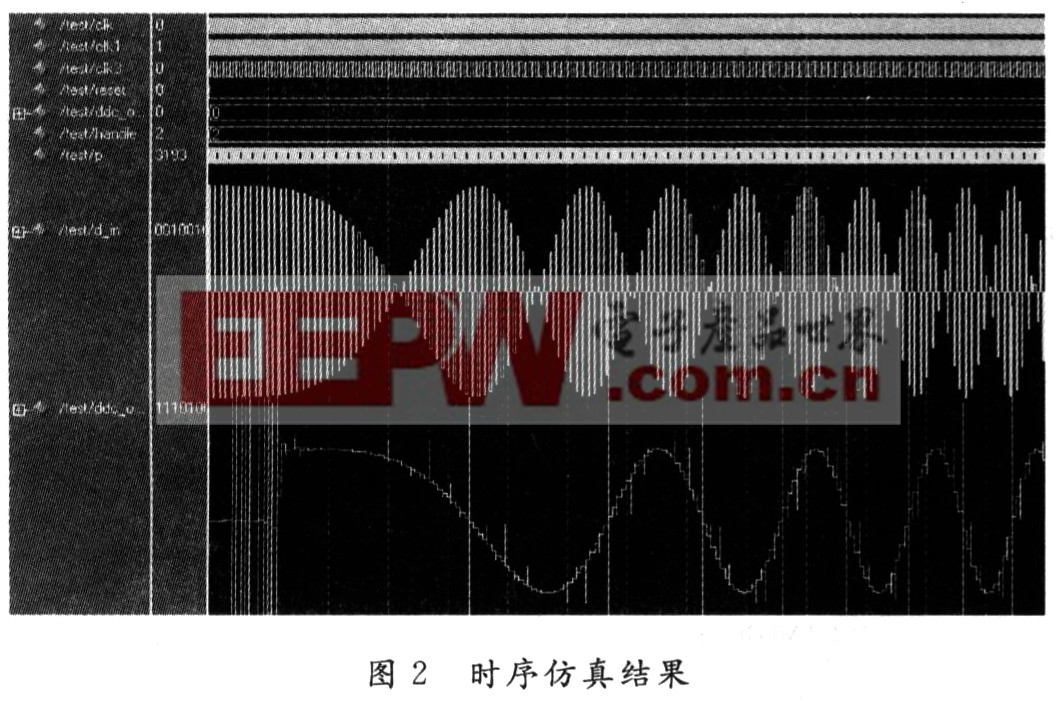

电路最大运行频率为176.15 MHz,满足要求。产生一个频谱带宽为5 MHz的扫频信号,将该信号用频率为70 MHz的余弦信号混频到中频处,将其采样后的值导入ModelSim 6.0中进行仿真,时序仿真结果如图2所示。

图2中上方为输入中频信号,下方为输出I路信号。由图可见,I路得到了原扫频信号,验证了设计的正确性。

下面考虑另一种下变频方案进行比较。如果对相同的信号以60 MHz的速率进行采样,则NCO的频率为10 MHz,正余弦样本值的周期为6,需要用到两个乘法器进行混频,设计出的滤波器阶数也增加了。布局布线后消耗的FPGA资源超过了前面的设计。

5 结 语

由以上讨论可知,选择合适的采样率的好处如下:

(1)可以减少NCO的样本值数,从而减少混频时的资源消耗;

(2)可以简化抽取滤波器的设计。

同时,使用基于并行DA算法的滤波器,则可以用较小的硬件资源实现高速率的滤波功能。正是基于以上优点,本文设计的数字下变频方案以较少的资源完成了信号的数字下变频,有重要的实用价值。

评论