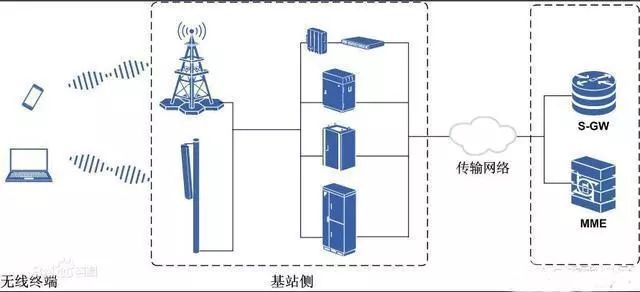

TMS320TCI6612/14 助力小型蜂窝基站实现高性能

该 TCI6612/14 与之前推出的 TCI6616 和 TCI6618 无线基站 SoC 软件兼容,设计人员可轻松设计出支持所有 2G、3G 以及 4G 标准的多模式基站。这种高灵活性不仅可帮助 OEM 厂商简化升级到 4G 的工作,同时还可帮助基站 OEM 厂商以比同类竞争解决方案更低的成本在更短的时间内开发出更丰富的解决方案。TCI6612 与 TCI6614 引脚兼容,可帮助制造商在单个硬件设计的基础上,提供多种量身定制的解决方案。

专为小型蜂窝基站精心设计的 TCI6612/TCI6614 高性能解决方案

TCI6612 和 TCI6614 SoC 专为小型蜂窝无线基础设施基带应用而精心设计,堪称小型蜂窝基站的理想解决方案。此外,这两款 SoC 还可实现支持 GSM、CDMA、WCDMA、TD-SCDMA、WiMAX、FDD-LTE 以及 TDD-LTE 等应用的基带解决方案。TCI6612 和 TCI6614 代码向后兼容,不但支持软件重复使用,还可维护增值设计与 IP,从而可简化从 C6000TM DSP 的升级。此外,TI TCI6612 与 TCI6614 还充分利用 KeyStone 架构进行扩展,能够满足从单区段小型蜂窝到多区段宏蜂窝等所有基站的需要。凭借可驱动各种基站产品的单软件库,开发人员将实现最高的研发效率以及最低的产品成本。

TCI6612 和 TCI6614 采用 40 纳米工艺技术,可实现达 4.8GHz 的原始 DSP 处理能力以及每秒高达 153.6 个 16 位 GMAC 的性能,因此这两款器件均是高性能 DSP 编程难题的低成本解决方案。TCI6612 和 TCI6614 均具有强大的浮点处理能力,可提供每秒高达 768 亿次的浮点运算 (GFLOP) 性能,是业界功能最强大的浮点和定点 SoC。TCI6612 和 TCI6614 在同一内核上整合了定点与浮点两种处理功能,可实现比独立定点实施方案快 5 倍的速度。此外,复杂算法的开发及调试时间可从数月锐减到数天。TCI6612 集成 2 个 C66x DSP 核,而 TCI6614 则具有 4 个 C66x DSP 核,适用于较大的小型蜂窝基站设计。

TCI6612 和 TCI6614 集成了按 2 层存储器系统排列的大型片上存储器,其可最大限度地减少时延,提升系统性能。两款器件中每个内核的 层1 (L1) 程序与器件上的数据存储器容量均为 32KB。层 2(L2) 存储器可在程序与总容量为 4,096KB(每个内核为 1,024KB)的数据空间之间共享。它们包含 2,048KB 的多核共享存储器 (MSM),可用作共享的 L2 SRAM 或共享的 L3 SRAM。专用多核共享存储器控制器 (MSMC) 不但可防止内核间出现存储器争用,而且还可在核内与其它 IP 模块之间判断对共享存储器的访问。

TCI6612 与 TCI6614 具有高性能外设集,可为开发各种不同覆盖范围与容量的高健硕基站提供所需的一切。包括:

l I²C、SPI 以及 UART;

l 可为支持 GEN1 与 GEN2 提供 2 个通道的 PCI Express 端口;

l 12 个 64 位通用定时器(也可配置为 16 个 32 位定时器);

l 具有可编程中断/事件生成模式的 32 位通用输入/输出 (GPIO) 端口;

l 针对硬件加速分派的 Multicore Navigator;

l 符合 RapidIO 2.1 规范的 4 通道串行 RapidIO® (SRIO),支持每通道达 5Gbps 的工作速率;

l 64 位 DDR3 SDRAM 接口;

l 16 位外部存储器接口 (EMIF),可连接闪存(NAND 和 NOR)及异步 SRAM;

l 基于 SERDES 的第二代天线接口 (AIF2),具有 6 个高速串行链路,每个链路支持高达 6.144Gbps 的工作速率,符合 OBSAI RP3 与 CPRI 标准。

为实现器件与网络之间的高效率通信,TCI6612 和 TCI6614 包含了由以下组件构成的网络协处理器:

l 2 个 10/100/1000 以太网媒体接入控制器 (EMAC),可在 DSP 核处理器与核心网络之间提供一个高效率接口;

l 管理数据输入/输出 (MDIO) 模块(也是 EMAC 的组成部分),用于不断轮询所有 32 个 MDIO 地址,以列举系统中所有的 PHY 设备;

l 用于实现 L2 至 L4 功能分类的数据包协处理器,处理速率高达 1.5Gbps;

l 安全加速器模块,能够通过 IPSec、SRTP 以及 3GPP 无线接口安全协议对 1Gbps 以太网流量进行连线速度处理;

l 允许多个设备通过 SGMII 连接的嵌入式以太网交换机,无需板级以太网交换机。

TCI6612 和 TCI6614 高性能嵌入式处理器可执行无线基站应用常见的密集型信号处理功能,可提升整体系统性能,而且频谱效率也较常规解码技术高出 40%。

位速率协处理器提升频谱效率

位速率协处理器 (BCP) 是一个多标准加速引擎,一旦启用 BCP,便可接管无线信号链中所有的位速率处理工作,无需 DSP 核参与。BCP 内含调制器、解调器、交错器/解交错器、涡轮及卷积编码、速率匹配器/速率解匹配器、分组码解码相关器以及 CRC 引擎。BCP 不但可为 MIMO 均衡消除干扰,而且还支持高性能 PUCCH 格式 2 解码。它可接管大约 15GHz 的 CPU MIPS。这些技术与 TI 新一代 DSP C66x 内核强大的 MIMO 处理功能相结合,可为运营商与用户等提供可兑现 4G 承诺的 SoC。

更快的协处理器可优化基站设计

自 2001 年以来,TI 已经提供了多种由可配置硬件加速器组成的无线电协处理功能,用于接管处理需求,提升整体系统性能。此外,TI 协处理器还可降低基站电源需求与消耗,以及电路板复杂性,从而可简化新产品的设计、构建和部署。

协处理器 | 总体性能(1.2-GHz 内核频率下) |

FFT/DFT | MSPS @ 256-FFT MSPS @ 192-DFT |

涡轮解码 | LTE – Mbps @ 6144 block size, 6 iterations WCDMA – Mbps @ 5114 block size |

涡轮编码 | LTE/WCDMA 1.6 Gbps |

维特比解码器 | >38 Mbps (K = 9) Mbps |

耙式搜索加速器 | 每周期 32 位倍增 |

WCDMA 解扩 | 可在 8 路径下支持 256 个 AMR 用户 |

WCDMA 扩频 | 采用 2 组无线电链路支持 256 个 AMR 用户,并在 1 Gbps 下支持 1.5 分集数据包 |

网络协处理器 | 2.8 Gbps |

BCP | LTE – DL 2.2 Gbps, UL 1.1 Gbps WCDMA – DL: 800 Mbps, UL 400 Mbps |

随着无线标准的演进和相关实施的标准化,TI 无线 SoC 的每一次演进都让协处理功能更加丰富,这可帮助我们的客户在实现更高性能基站解决方案的同时降低功耗与成本。TI 将 DSP 与 ARM 核同协处理器一起集成的 SoC 策略是实现无线基站 SoC 设计的最高效最经济的方法,其将继续保持市场领先解决方案的地位。TI 各种协处理器无需外部 FPGA 与 ASIC,便可实现 3G 与 4G 基站的高性能。

评论