基于FPGA的移动通信中卷积码编码器设计

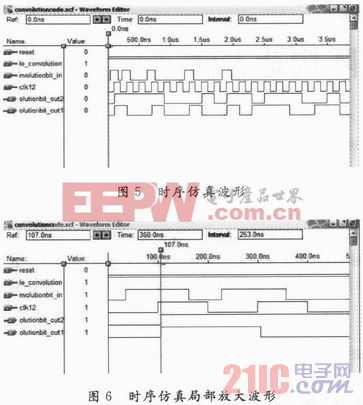

3.2 时序仿真

在不考虑时延的情况下,对照图4与图5,两者仿真波形一样。从图6可以看出卷积编码器的时延为7.0 ns,这是因为功能仿真不考虑信号时延等因素,而时序仿真则是选择了具体器件并完成布局布线后进行的含定时关系的仿真,所以其仿真更接近真实器件运行特性,因而仿真精度更高。由于不同器件的内部时延不一样,不同的布局,布线方案也会给时延造成很大的影响,因此在设计实现后,有必要对网络和逻辑块进行时延仿真,分析定时关系,估计设计性能。本文引用地址:https://www.eepw.com.cn/article/154639.htm

时序仿真后,再进行器件编程和调测。实测结果完全正确,达到了设计要求。

4 结语

本文阐述了卷积码编码器的工作原理,利用FPGA器件,设计出了(2,1,9)卷积码编码器。仿真及测试结果表明,达到了预期的设计要求,并用于实际项目中。

评论