ARM系统中DMA方式在数据采集中的应用

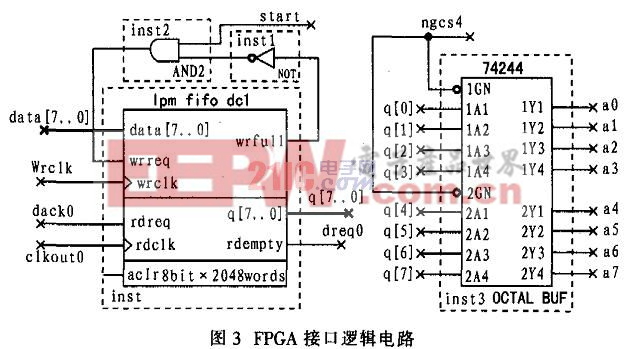

这里主要介绍DMA方式的数据采集,FPGA内部的CCD驱动逻辑暂不介绍。FPGA与ARM的接口逻辑电路如图3所示。

FPGA内部采用异步FIFO解决CCD输出数据频率和S3C2410采集频率不匹配的问题,写时钟由CCD输出位同步信号提供,读时钟由S3C2410的时钟输出引脚CLKOUT0提供。CLKOUT0根据ARM内部寄存器的设置可以输出不同的时钟频率。FIFO输出数据经过以nGCS4为选通信号的BUFFER后接到ARM的数据总线上。nGCS4是S3C2410存储空间中BNAK4的片选信号,当S3C2410对地址范围

0x20000000~0x28000000的存储空间进行读写操作时,BANK4为低电平,其余时间均为高电平.用它作为BUFFER的选通信号能有效地避免数据总线的污染。

FIFO的写请求信号由S3C2410与FIFO的满状态共同控制。当ARM发出START信号并且FIFO未满时,写请求信号为高电平。FIFO在写时钟的控制下写入数据。当START信号撤销或者FIFO满时,写请求信号变为低电平,停止写操作。

FIFO的读操作与ARM的DMA操作配合进行。系统采用单服务命令模式的DMA操作,每次传输一个字节数据位。当DREQ0信号变为低电平时DMA操作开始,每次传输一个字节后产生一个DACK0应答信号,而且只要DREQ0为低电平DMA操作就继续进行,直到DMA控制寄存器中的计数器为0.产生DMA中断。根据上述时序特点,将FIFO的空信号作为DMA的请求信号DREQ0.当CCD输出的数据写入FIFO中时,空信号跳变为低电平启动DMA操作,同时以DACK0信号作为FIFO的读请求。每一次DMA传输完成后应答信号使FIFO的读指针移动一位,以实现数据的快速准确采集。本文引用地址:https://www.eepw.com.cn/article/151953.htm

4 Linux下的驱动程序设计

系统采用ARM+嵌入式Linux的构架,Linux版本为2.4.18,采集系统必须和高效灵活的接口驱动程序相结合才能在操作系统下正常工作。

4.1 驱动程序的基本概念

设备驱动程序是操作系统内核和硬件之间的接口,它属于内核一部分,主要功能如下:

(1)对设备初始化或释放;

(2)把数据从内核传送至硬件。从硬件读取数据:

(3)读取应用程序传送给设备的数据,回送应用程序请求的数据:

(4)监测和处理设备出现的异常。

设备驱动程序为应用程序屏蔽了硬件的细节,在应用程序中,硬件设备只是一个设备文件,可以像操作普通文件一样对硬件设备进行操作。

4.2 修改代码

嵌入式Linux在arch/arm/mach-s3c2410目录下的dma.c文件中定义了一些与DMA操作相关的通用函数,主要有:申请DMA通道函数s3c2410_re,quest_dma()、申请DMA中断函数request_irq()、加入DMA队列函数s3c2410_dma_queue_buffer()、进行DMA操作函数process_dma()以及中断处理程序dma_irq_handler()等。在进行特定接口操作时,必须对其进行适当的修改。根据接口设置修改如下内容:

增加外部DMA操作的寄存器设置:

#define XDREQ0_CTL(DEMAND_MODE | SYNC_HCLK | INT_MODE |TSZ_UNIT

| SINGLE_SERVICE | HWSRC(CH0_nXDREQ0) | DMA_SRC_HW | CLR_ATRELOAD | DSZ(DSZ_BYTE)| TX_CNT(0));

//设置DMA为单服务命令模式,8位数据总线、允许中断且通过DREQ0硬件触发DMA操作

评论