基于DSP的1553B总线系统设计与实现

3.3 逻辑综合电路

BU-64843和F2812之间的逻辑综合电路由FPGA完成。本系统的可编程逻辑器件采用Xilinx公司Spartan-3系列的FPGA芯片XC3S400,该芯片的I/O口供电电压为3.3 V、系统门数为40万、最大可用I/O数为264个。逻辑综合电路包括:地址译码电路、逻辑控制电路。地址译码电路功能是对接口卡所使用的F2812存储器和BU-64843存储器进行地址选择、译码。译码程序在Xilinx ISE 9.2i环境下用硬件描述语言Verilog-HDL编写。选用FPGA作为逻辑综合电路的另一个优点是:VerilogHDL程序的烧写通过JTAG接口完成,除了一条烧写线外不需要任何附加的硬件电路,因此只要硬件连接正确,其余的工作均由软件完成,便于以后的系统升级。VerilogHDL程序根据F2812的地址总线、数据总线和片选信号,经逻辑译码产生BU-64843的片选信号SELECT#,寄存器和缓冲区选择控制信号MEM/REG#。

逻辑控制电路功能是产生BU-64843所需要的控制信号以及给F2812提供中断信号、握手信号、插入等待信号。由F2812和BU-64843向XC3S-400提供地址线、数据线、中断申请线、中断响应线以及读、写信号线。本文引用地址:https://www.eepw.com.cn/article/151369.htm

4 驱动软件的设计

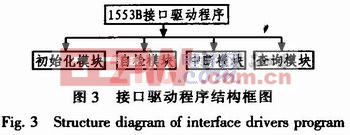

驱动程序的编写采用C语言与汇编语言混合编程的实现方法,兼顾二者的优点,使程序既有C语言较好的可读性和可移植性,又有汇编语言较高的效率。驱动程序的功能主要是实现BU-64843协议芯片的初始化、RAM空间的自检、与上位机的通信、中断响应、总线数据的读取和发送。驱动程序从本质上说,就是根据上位机的命令和要求,控制接口卡的工作,实现系统的启动、停止、自检以及自检结果的返回等,在系统启动后主要实现1553B总线数据的接收和发送。整个驱动程序的组成如图3所示。

4.1 初始化模块设计

在驱动程序编制中,初始化模块是非常重要的一部分,作为整个程序的入口,初始化模块完成整个接口卡的初始配制,该模块主要功能为:

1)完成对F2812初始化,设置其相关寄存器,主要是设置有关中断和串口的寄存器,包括中断标志寄存器(IFR)、中断使能寄存器(IER)、中断控制寄存器(ICR)、SCI通信控制寄存器(SCICCR)、SCI控制寄存器l(SCICTL1)、波特率设置寄存器(SCIBAUD)等,以确定中断源和串口的波特率、停止位等。其具体操作为:①使IFR=Ox0000。IER=Ox0000,关闭所有的中断;②使IER=OxO101,开启中断SCITXRXINT和中断XINTl;③使ICR=0x001F,将中断模式设置为下降沿触发中断XINTl;④使SCICCR=0x0007;设置发送和接收中使用1 bit停止位,8 bit字符长度;⑤使SCICTL1=0x0003;使能发送器TX、接收器RX;⑥使SCIBAUD=Ox01E7,系统时钟SYSCLK的频率为150 MHz,低速外设时钟频率LSPCLOCK为37.5 MHz时,异步串行口数据传送波特率为9 600 b/s,BRR的数值可由下面的公式得到:

⑦SCICTL1=0x0023,使SCI退出复位。

2)完成对BU-64843协议芯片内部寄存器(主要包括开始/复位寄存器、配置寄存器1、配置寄存器2、配置寄存器3、中断屏蔽寄存器)的初始化设置,使其能够正确实现BC模式的功能。BU-64843对片内功能寄存器的设置顺序有严格要求,如果顺序不正确将会引起芯片初始化失败。BU-64843工作在BC模式下的有关寄存器的配置顺序如下:①将开始,复位寄存器配置为0x0001,即可对BU-64843进行软件复位;②如果用到BU-64843增强模式,将配置寄存器3配置为Ox8000;③将中断屏蔽寄存器设置为Ox0001,使消息完成中断使能;④将配置寄存器1设置为BC模式;⑤将配置寄存器2设置为0x0008,使中断方式为低电平中断;⑥将开始/复位寄存器配置为Ox0002,启动BC传输模式。

评论