基于DSP的1553B总线系统设计与实现

3 接口电路的硬件设计

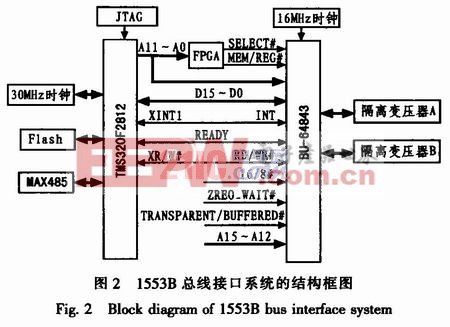

系统的硬件电路主要包括:DSP模块、1553B总线接口模块、逻辑综合模块。系统的结构框图如图2所示。

3.1 DSP模块

DSP芯片功能强、体积小、使用方便灵活,被众多领域广泛应用。F2812是TI公司推出的采用高性能静态CMOS技术的32位定点数字信号处理器,器件上集成了多种先进的外设,为现代控制领域应用提供了良好的控制核心。F2812的地址线为19位,数据线为16位。其特点有:1)采用高性能静态CMOS技术,其供电电压为3.3 V,采用哈佛总线结构和流水线操作,具有150 MIPS的运算能力,可单周期执行32位×32位的乘和累加操作(MAC)或双16位×16位MAC运算;2)片上存储器包括128 k×16 Flash存储器、18 k×16的片内RAM、4 k×16的Boot ROM大容量的片内RAM可满足大多数设计要求,无需扩展片外存储器,既降低了成本又使硬件设计变得简洁;3)具有外部中断扩展(PIE)模块,可支持多达45个外部中断,最多可达56个的可编程通用输入/输出(GPIO)引脚,带有丰富的接口模块包括2个串行通信接口(SCI)、串行外设接口(SPI)和多通道缓冲串口(MeBSP),为建立信号处理平台提供基础。

3.2 1553B接口电路

传统的1553B接口卡设计时采用BU-61580接口芯片,采用70引脚的双列直插式组件(DIP)封装,5 V供电,考虑到本系统的DSP芯片F2812的I/O是3.3 V电平,所以1553B总线接口电路采用DDC公司的首款全3.3 V的1553B接口芯片BU-64843,无需电平转换,简化了硬件电路设计,采用该芯片80-pin陶瓷扁平封装更加方便用户进行硬件电路设计。BU-434843内部还集成了双收发器逻辑、编解码器、协议逻辑、内存管理和中断控制逻辑,支持BC/RT/MT模式,还提供了一个4 kB的内部共享静态RAM和与处理器总线之间的缓冲接口。

BU-64843与微处理器或外部存储器接口非常灵活,可与8位、16位多种微处理器相连接,并且可以实现无缝连接或者只需很少的粘和逻辑电路。BU-64843有2种工作模式:透明模式(TRANSPARENT)和缓冲模式(BUFFERED)。透明模式时芯片可以寻址64 KB,即可以寻址到其外部的RAM,这时需要为其配置外部RAM。一般应用透明模式时。在BU-64843协议芯片和CPU之间配置双口RAM。而在二者的数据总线和地址总线之间需要使用隔离器。缓冲模式时只寻址其内部的4 KB字的RAM,地址单向,可直接由CPU驱动,不需要使用总线隔离器。另外,BU-64843还根据微处理器是否具有READY(握手信号)选择零等待和非零等待方式。非零等待是指在微处理器对BU-64843进行并行总线(读、写)操作时,BU-64843内部逻辑电路若有操作时,微处理器需要等待BU-64843准备好。当BU-64843准备好时,就输出READY信号。在这种情况下。应将BU-64843的READY信号接到微处理器的READY信号上,并设置微处理器的等待方式受READY控制。16位缓冲模式是最常用的接口形式。提供一个与16位或32位微处理器共享RAM的缓冲器接口,在这种接口中,BU-64843的内部地址/数据缓冲器使其与微处理器的地址,数据隔离。一般在传输数据量比较少,BU-64843内的4 KB RAM足够用时。可选用16位缓冲非零等待模式。在该模式下将引脚16/8#置为高电平,TRANSPARENT/B-UFFERED#置为低电平,ZERO_WAIT#置为高电平。工作在缓冲方式下,占用16位数据总线和12位地址总线,其所有的控制信号由FPGA的译码电路产生,通过中断方式与F2812通信,因此BU-64843的中断引脚INT与F2812的外部中断XINTl连接;BU-64843总线接口有2个数据通道,通道A和通道B,这是为了保证通信的可靠性而采取的冗余设计,在实际的工程中也使用2个通道,通过软件选择任意通道进行数据传输。BU-64843通过2个耦合变压器PM-DB2755与外部的屏蔽双绞线连接:16 MHz有源晶振作为时钟输入。

评论