ARM和DSP设计的地震加速度信号处理系统

解调输出信号:

结合式(1)和式(3)即可求出加速度a(t).

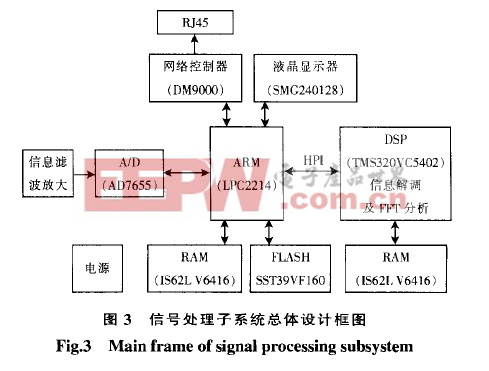

以ARM(选用飞利浦公司的LPC2214)和DSP(Ti公司的TMS320VC5402)为核心,外扩信号调理、A/D采集、网络控制及液晶显示模块.以ARM作为系统控制中心,控制A/D转换器进行地震加速度已调信号的采集,经DSP的HPI接口将数据存储到DSP内部RAM 中.完成解调信号的网络传输控制、实时显示以及TMS320VC5402的HPI引导装载.而DSP主要进行信号运算,完成解调和FFT频谱分析.

LPC2214控制器片内有16 kbits RAM和256 kbitsFLASHl 31.为了便于系统升级,扩展了128 kbits的外部RAM 和2 Mbits的外部FLASH.由于DSP要对大量的数据进行运算,而内部RAM 空间有限且还要用于存放上电复位后的boot loader程序,所以扩展128 kbits外部RAM.

LPC2214有bank。 bank 4个外部存储器组,而对于图3中的系统设计,ARM扩展的存储器或外部I/O器件有6个.所以利用片选信号CS3、地址线A23、A22、A21和一片138译码器进行地址空间细分,此片外存储器或I/O 器件属于bank,组, 所用地址为0x83000000~0x83ffffff。

3.1 信号调理及A,D采集电路

信号调理最主要目的是为了去除信号中的噪声,使被测电压范围和AD采样范围相匹配以提高采样精度.本系统选用Anolog Device公司的ADA4861—3专用放大芯片.该芯片集成了3路放大器.采用单5 V供电.通过调节外接电阻的阻值可以获得1~1 900的放大增益,输出具有良好的线性度和温度稳定性.由于放大电路集成在芯片中.故减少了噪声的引入.

选择MD芯片主要考虑的性能指标有分辨率、转换速率、输入通道数、信噪比、输出接口等参数.因为所采集的加速度信号频率在1 kHz以内..根据奈圭斯特定理采样频率 >2 kHz就能无失真地恢复原信号,输入信号有3路,综合考虑以上因素本系统选用Anolog Device公司生产的AD7655芯片.该芯片支持4路输入(INA1、INA2、INB。、INB2),转换位数达16位,1MSPS的转换速率,单电源+5 V供电,串/并口输出方式,双通道同步采样.采样由A。引脚电平控制,A0=0,INA1/INB1采样同步;A o=1,INA~NB2采样同步问.参考电压 面接2.5 V,分辨率为2×VREF/655 36,约为76-3 V.

干涉仪相关文章:干涉仪原理

评论