基于ARM的大型LED点阵显示系统的设计

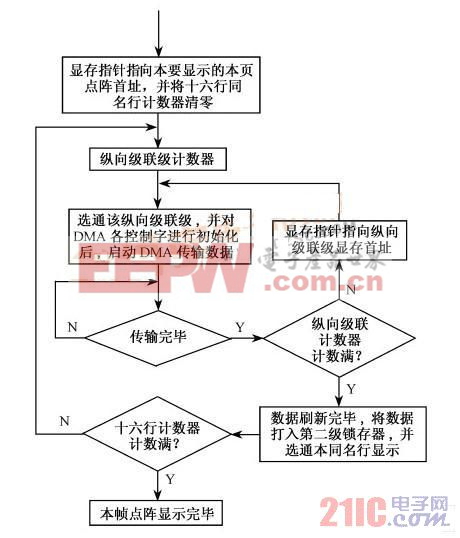

显示程序流程图

图4 显示程序流程图。

2.2 点阵排序

由于LED 显示模块的电路结构以及使用了16位并行总线和DMA 数据传输技术,在显示时点阵码的排放顺序,需要满足如下要求:

(1) 16 位并行总线一次数据传输,即一次DMA写操作传输两个字节的点阵码,低位和高位字节分别传送到两相邻的纵向级联模块的同名行和同名列数据锁存器中,因此相邻的纵向级联模块的同名行和同名列点阵码应连续存放。

(2) 由于显示模块的第一级列数据锁存器译码选通电路结构和DMA 数据传输要求,对同一显示模块的上下两部分的同名行点阵应按列数据锁存器的选通顺序依次连续存放。

(3) 两相邻的纵向级联级的一系列横向级联级应按(1) 和(2) 原则进行点阵码排序。

(4) 各纵向级联级依次按(1) 、(2) 、(3) 原则进行点阵码排序。

(5) 16行扫描显示方式下,一个大型LED 屏分为16 行同名行,每一同名行按照( 1) 、( 2) 、(3) 、(4) 原则进行点阵排序。

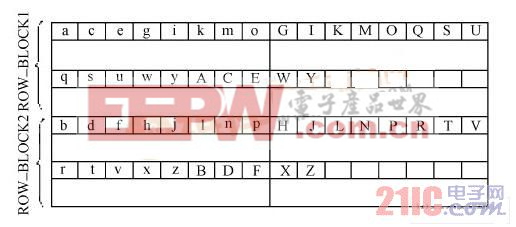

以一个128 ×64的点阵屏第一行同名行的数据排序为例,如图5所示,第一行同名行的点阵码的存放顺序应依次为: a,b,……z,A,B,……Z,……。

128 ×64点阵屏第一行同名行的数据排序图

图5 128 ×64点阵屏第一行同名行的数据排序图。

3 结论

使用并行总线DMA 数据传输技术简化了LED显示系统的软硬件设计,降低了系统成本,取得了很好的显示质量,在2211184MHz的系统时钟下,512 ×256 (8m2 ) 单色点阵屏显示帧频达到250Hz,平均120ns传送1个字节,达到了使用单CPU系统代替多机系统控制LED显示系统的目的。但为了使上一代的显示驱动板仍能够使用,点阵码需要排序,显示时只能使用页面方式显示,这样在多页动态滚屏显示时需要大容量的存储器。对于512 ×256单色点阵屏需要数十兆的容量,使用32 位ARM7TDMl内核先进控制器S3C44B0X和廉价的大容量SDRAM存储器可以使该问题得到很好的解决。若使用针对DMA控制显示设计的显示驱动板显示时,点阵码就不需要排序,一片数百KB 的SRAM就能满足系统要求了。

本文引用地址:https://www.eepw.com.cn/article/151128.htm

评论