基于闪存的大容量存储阵列

由于NAND Flash特殊的基本结构,在进行读写操作的时候,外部控制器不能通过普通总线的形式对其内部某一位进行操作,而是以页为最小操作单位,在擦除操作时以块为最小操作单位。

对NAND Flash芯片内部的某一页进行操作时,要先将操作命令字和地址信息写入,芯片才会根据操作命令字对给定地址的存储单元进行相应的操作。芯片的主要操作命令字可以查阅芯片手册。

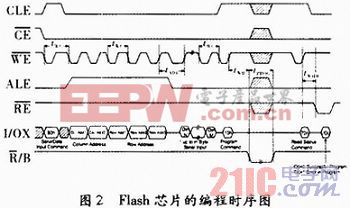

K9KAG08UOM的页编程写入时序图如图2所示,其中写周期tWC最小为25 ns;地址到数据加载的延迟时间tADL最小为75 ns;编程命令到编程开始的延迟时间tWH最大为100 ns;编程时间tPROG的典型值为200μs。本文引用地址:https://www.eepw.com.cn/article/149176.htm

设Flash芯片一页的容量为4 224 Byte,按典型时间计算,完成一页编程写入所需时间约为

6×25 ns+75 ns+4 224×25 ns+100 ns+300μs=405.95μs

其中,编程命令和数据传送的总时间为105.95 s,编程时间为300 s。单片K9KAG08UOM最高数据存储速率为

4 224/405.95μs=10.405 B·μs-1=10.405 MB·s-1

上述时间是按照最高速度计算的,实际使用时单片存储器的数据存储速率会小于它。如果留有足够的裕度,单片数据存储速率按照5 MB·s-1考虑,则对于200MB·s-1的要求,需要40片存储器并行工作,才能满足实时存储的要求。

2 FPGA芯片的选型

存储器阵列控制单元利用高性能FPGA实现,它对器件速度的要求不高,主要是必须提供足够的IO引脚,具体要求如下:(1)输入LVDS通道数为16+2,其中接收8个,发送8个,高速时钟2个通道。(2)输入读写速度:>200 MHz。(3)输出LVTTL电平的IO数为(80+24)x 4,其中数据80位,控制信号12位。(4)命令地址等其它低速信号线为14线。(5)输出读写速度>20 MHz。(6)引脚需求数:(16+2)×2+104×4+4+10=466。

拟采用Xilinx公司的Virtex-4系列FPGA可以满足设计要求,如XC4VLX80。其相关技术参数:(1)18 kBRAM模块:200个,3 600 kB。(2)内部存储器读写速度>500 MHz。(3)LVDS通道数为384。(4)用户可利用的IO引脚数为768。

3 FPGA控制逻辑设计

3.1 并行的NAND接口的设计

并行操作可以按照需要将多片闪存芯片的数据线结合起来共同使用,以此提高系统读写带宽和读写效率。在并行系统中,引进模块化的思想,即将多片闪存芯片当作一个模块,把这个模块作为整个系统最小的数据存储单元,任何操作都是面向这些模块来进行。也就是说,多片闪存芯片作为一个整体,对外输出8×n位的数据。同时,并行操作也大大提高了系统的操作速度。以下以写4 kByte的数据进入一个由5片闪存芯片组成的的模块为例:当只对一片闪存芯片操作时,典型的写入时间为200μs。但当闪存芯片模块进行操作时,由于是对模块内的5片芯片进行同时写入,因此系统的整体操作速度提高了4倍。

并行操作的实现依赖于并行的NAND接口的设计。板卡中采用的K9WBG08U1M的IO位宽为8 bit。由上节的分析可知,对于200 MB·s-1的要求,需要40片存储器并行工作,才能满足实时存储的要求。板上共载有40片NAND,分为4组,每组10片存储芯片,则单板容量为40×单片存储容量4 GB。为满足信号驱动特性的要求,每5片Flash存储芯片由FPGA单独驱动。

评论