楷登电子(美国 Cadence 公司) 今日宣布其数字、签核与定制/模拟工具成功在三星电子公司7LPP和8LPP工艺技术上实现。较前代高阶工艺节点FinFET技术,7LPP和8LPP工艺技术不仅进一步优化了功耗、性能和面积特性,扩展能力也更为出色。目前,客户已经可以应用下一代技术开始早期设计。 Cadence定制/模拟、数字和签核工具全面满足三星工艺需求,支持实现7LPP和8LPP工艺技术;三星客户可开发各类复杂的高阶节点设计,充分满足移动市场和其他垂直市场的应用需求。

关键字:

Cadence 7LPP

作者 王莹 近日,Cadence发布了首款面向汽车、监控、无人机和移动市场的神经网络DSP IP,引起了业界的关注。 Cadence公司Tensilica事业部资深市场群总监Steve Roddy专程来到北京,向媒体介绍其特点。 在神经网络的器件方面,英伟达主宰了通用GPU。此次Cadence Tensilica发布的神经网络DSP IP则是面向嵌入式芯片。 通常其他友商的方案是面向一个卷积神经网络(CNN)层,而最新的Cadence Tensilica Vision C5 DSP由于可配置,可以面

关键字:

Cadence 神经网络DSP IP Steve Roddy 201706

近日,Cadence发布了首款面向汽车、监控、无人机和移动市场的神经网络DSP IP,引起了业界的关注。 实际上,多家公司正在推出或研制神经网络IP、c/解决方案。Cadence的方案有何优势?Cadence公司Tensilica事业部资深市场群总监Steve Roddy为此专程来到北京,向媒体介绍其特点。 Vision C5概况 在神经网络的器件方面,英伟达主宰了通用GPU。此次Cadence Tensilica发布的神经网络DSP IP则是面

关键字:

Cadence 芯片

楷登电子(美国Cadence公司)今日正式公布业界首款独立完整的神经网络DSP —Cadence® Tensilica® Vision C5 DSP,面向对神经网络计算能力有极高要求的视觉设备、雷达/光学雷达和融合传感器等应用量身优化。针对车载、监控安防、无人机和移动/可穿戴设备应用,Vision C5 DSP 1TMAC/s的计算能力完全能够胜任所有神经网络的计算任务。如需了解更多内容,请参访www.cadence.co

关键字:

Cadence DSP

楷登电子(美国 Cadence 公司)今日宣布,凭借Cadence® ProtiumÔ S1 FPGA原型验证平台,晶晨半导体(Amlogic)成功缩短其多媒体系统级芯片(SoC)设计的上市时间。基于Protium S1平台,晶晨加速实现了软/硬件(HW/SW)集成流程,上市时间较传统软硬件集成工艺缩短 2 个月。如需了解Protium S1 FPGA原型设计平台的详细内容,请访问www.cadence

关键字:

Cadence Protium

楷登电子(美国Cadence公司)今日正式发布针对7nm工艺的全新Virtuoso® 先进工艺节点平台。通过与采用7nm FinFET工艺的早期客户展开紧密合作,Cadence成功完成了Virtuoso定制设计平台的功能拓展,新平台能帮助客户管理由于先进工艺所导致的更复杂的设计以及特殊的工艺效应。新版Virtuoso先进工艺平台同样支持所有主流FinFET先进节点,性能已得到充分认证;同时提高了7nm工艺的设计效率。

为了应对7nm设计的众多技术挑战,Virtuoso先进工艺平台提供丰富

关键字:

Cadence Virtuoso

PCB设计软件就是以电路原理图为根据,实现电路设计所需的功能。电路板的设计主要指版图设计,需要考虑元器件和连线的整体布局,包括内部电子元件的优化布局;金属连线和通孔的优化布局;电磁防护;散热等各种因素。优秀的PCB设计能够达到良好的电路性能和散热性能,节约生产成本。PCB设计需要借助计算机辅助设计(EDA)实现。下面介绍几款国内流行的PCB设计软件。

Protel/Altium Designer

国内低端设计的主流,简单易学,适合初学者。国内使用protel还是有相当有市场,毕竟小公司

关键字:

PADS Cadence

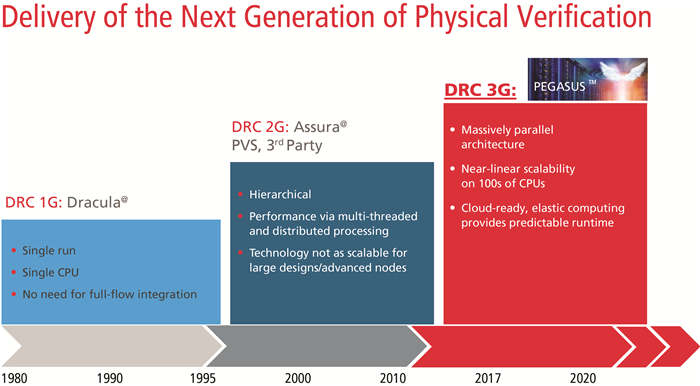

楷登电子(美国 Cadence 公司)今日正式发布Pegasus™验证系统,该云计算(cloud-ready)大规模并行物理签核解决方案将助工程师缩短先进节点IC的上市时间。Pegasus™验证系统解决方案是全流程Cadence数字设计与签核套件的新成员,可扩展至数百CPU,设计规则检查(DRC)性能最高可提升10倍,周转时间较上一代Cadence® 解决方案由数日降至数小时。如需了解Pegasus验证系统的详细内容,请参访www.cadence.com/go/pegas

关键字:

Cadence Pegasus

楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日正式宣布与台湾积体电路制造股份有限公司(TSMC)取得的多项合作成果,进一步强化面向移动应用与高性能计算(HPC)平台的7nm FinFET工艺创新。Cadence® 数字签核与定制/模拟电路仿真工具获得TSMC 7nm工艺 v1.0设计规则手册(DRM)认证及SPICE认证。合作期间,Cadence开发了包括多种解决方案的全新工艺设计包(PDK),进一步实现功耗、

关键字:

Cadence 7nm

楷登电子(美国 Cadence 公司)今日正式公布其与台湾积体电路制造股份有限公司(TSMC)全新12nm FinFET紧凑型(12FFC)工艺技术开发的合作内容。凭借Cadence® 数字与Signoff解决方案、定制/模拟电路仿真解决方案及IP,系统级芯片(SoC)设计师可以利用12FFC工艺开发正在快速发展的中端移动和高端消费电子应用。上述应用对PPA性能(功耗、性能和面积)的要求更高,为此,Cadence正与12FFC工艺的早期客户开展紧密合作。 Ca

关键字:

Cadence TSMC

楷登电子(美国 Cadence 公司)今日宣布,将与移动IoT公司CommSolid展开合作,为超低功耗移动通讯环境开发度身定制的全新基带 IP,并结合最新发布的 3GPP 窄频带物联网(NB-IoT)通讯标准,发力迅速发展的移动IoT市场。 CommSolid将单颗Cadence® Tensilica® Fusion F1 DSP与其最新CSN130基带解决方案集成,用于超低功率modem运行;以及包括语音触

关键字:

Cadence NB-IoT

楷登电子(美国 Cadence 公司)今日宣布,Methods2Business(M2B)的全新Wi-Fi HaLow™ MAC IP搭载Cadence® Tensilica® Fusion F1 DSP。该可授权IP为智能家居、智能城市和工业应用领域的SoC量身打造,是采用电池供电传感器节点的理想解决方案。凭借Fusion F1 DSP,M2B得以在实现IEEE 802.11ah&

关键字:

Cadence Wi-Fi

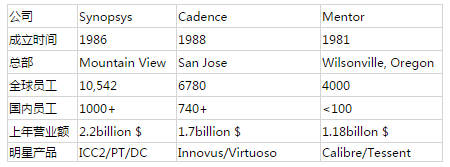

EDA是IC 设计必需的、也是最重要的武器。随着IC设计复杂度的提升,新工艺的发展,EDA行业有非常大的发展空间。

关键字:

EDA Cadence

楷登电子(美国 Cadence 公司)今日发布全新基于FPGA的Protium™ S1原型验证平台。借由创新的实现算法,平台可显著提高工程生产效率。Protium S1与Cadence® Palladium® Z1企业级仿真平台前端一致,初始设计启动速度较传统FPGA原型平台提升80%。Protium S1采用Xilinx® Virtex™ UltraScale™ FPGA技术,设计容量比上一代平台提升

关键字:

Cadence Protium S1

楷登电子(美国 Cadence 公司)今日发布业界首款已通过产品流片的第三代并行仿真平台Xcelium™ 。基于多核并行运算技术,Xcelium™ 可以显著缩短片上系统(SoC)面市时间。较Cadence上一代仿真平台,Xcelium™ 单核版本性能平均可提高2倍,多核版本性能平均可提高5倍以上。Cadence® Xcelium仿真平台已经在移动、图像、服务器、消费电子、物联网(IoT)和汽车等多个领域的早期用户中得到了成功应用,并通过产品流

关键字:

Cadence Xcelium

cadence介绍

EDA仿真软件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473