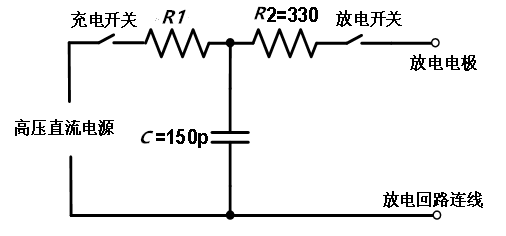

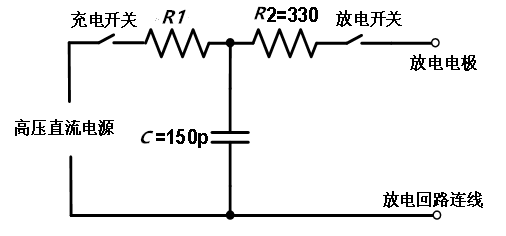

- ESD一直是电气和电子元件产品的主要关注点和突出威胁。在系统级ESD测试过程中,通常用静电枪来模拟ESD放电场景,放电电流波形必须符合IEC 61000-4-2标准。但标准给的误差范围较大,较大的误差会影响仿真结果的准确性。本文在Cadence下建立了静电枪电路模型,包括接触放电模型和HBM模型,具有较高的精确性。模型产生的电流波形与实际测试电流波形吻合性较好,验证了模型的准确性。该电路模型为静电放电仿真提供了一个新的激励源。

- 关键字:

202008 静电放电 Cadence 电路模型 静电枪

- 随着科技应用走向智能化、客制化,系统复杂度明显增长,IC设计业者要抢占车用、通讯或物联网等热门市场,以强大运算力实现快速验证与设计已不足够,部署弹性和整合资源将成为开发的关键考虑,云端部署会是重要的一步棋。通讯、车用和物联网是未来IC应用的主要场域,尤其随着持续开发人工智能应用,以及扩大部署5G、Wi-Fi 6等新一代网络技术,这些颇具潜力的应用展现了强劲成长。根据市调机构IC Insights上(6)月公布的研究显示,消费性及通讯IC类仍居IC市场最高市占率,至2024年预计将达35.5%,在近20年来

- 关键字:

Cadence 台积电 EDA IC设计

- Cadence Design Systems, Inc.宣布与台积电及微软三方合作之成果。该合作的重点是利用云端基础架构来缩短半导体设计签核时程。透过此合作,客户将可藉由微软 Azure上的Cadence CloudBurst平台,采用台积电技术的Cadence Tempus时序签核解决方案及Quantus提取解决方案,获得加速完成时序签核的途径。台积电设计建构管理处资深处长Suk Lee表示:「半导体研发人员正以先进的制程技术来实现与满足超过其功率及效能上的要求。但在日益复杂的先进制程签核要求下,使得实

- 关键字:

Cadence 台积电 微软 IC设计

- 联华电子今(6日)宣布Cadence®模拟/混合信号(AMS)芯片设计流程已获得联华电子28纳米HPC+工艺的认证。 透过此认证,Cadence和联电的共同客户可以于28纳米HPC+工艺上利用全新的AMS解决方案,去设计汽车、工业物联网(IoT)和人工智能(AI)芯片。 此完整的AMS流程是基于联电晶圆设计套件(FDK)所设计的,其中包括具有高度自动化电路设计、布局、签核及验证流程的一个实际示范电路,让客户可在28纳米的HPC+工艺上实现更无缝的芯片设计。Cadence AMS流程结合了经客制化确认的类比

- 关键字:

Cadence 联电 28纳米HPC 工艺中模拟/混合信号 流程认证

-

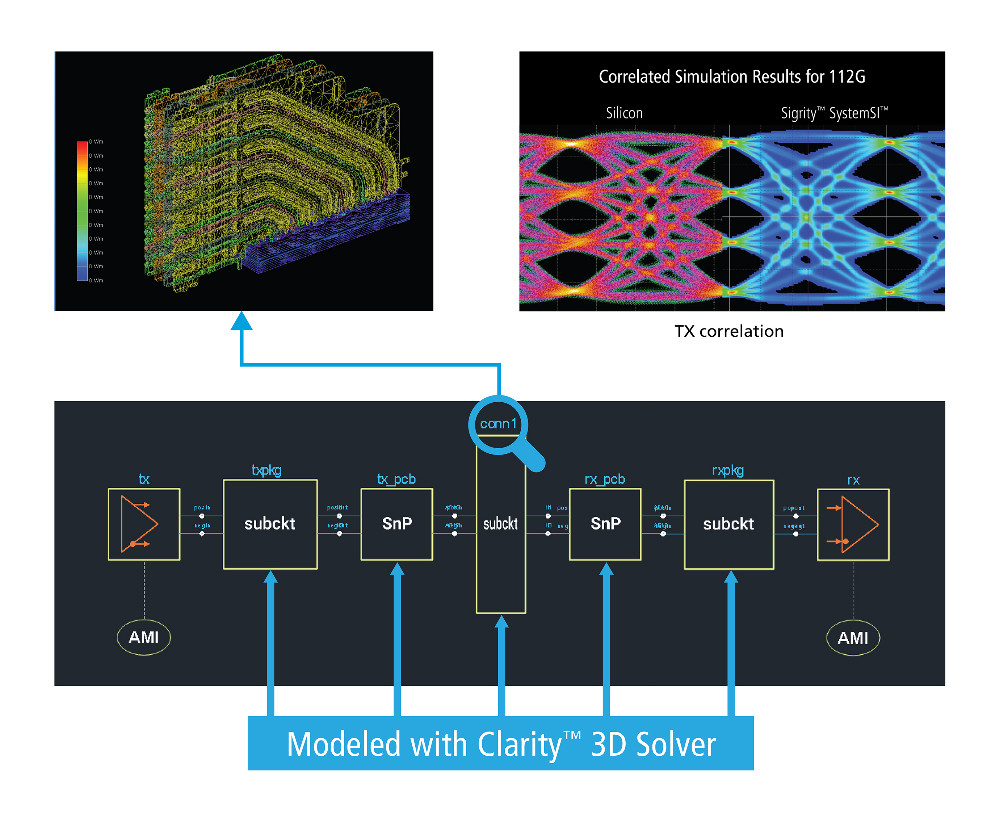

内容提要:

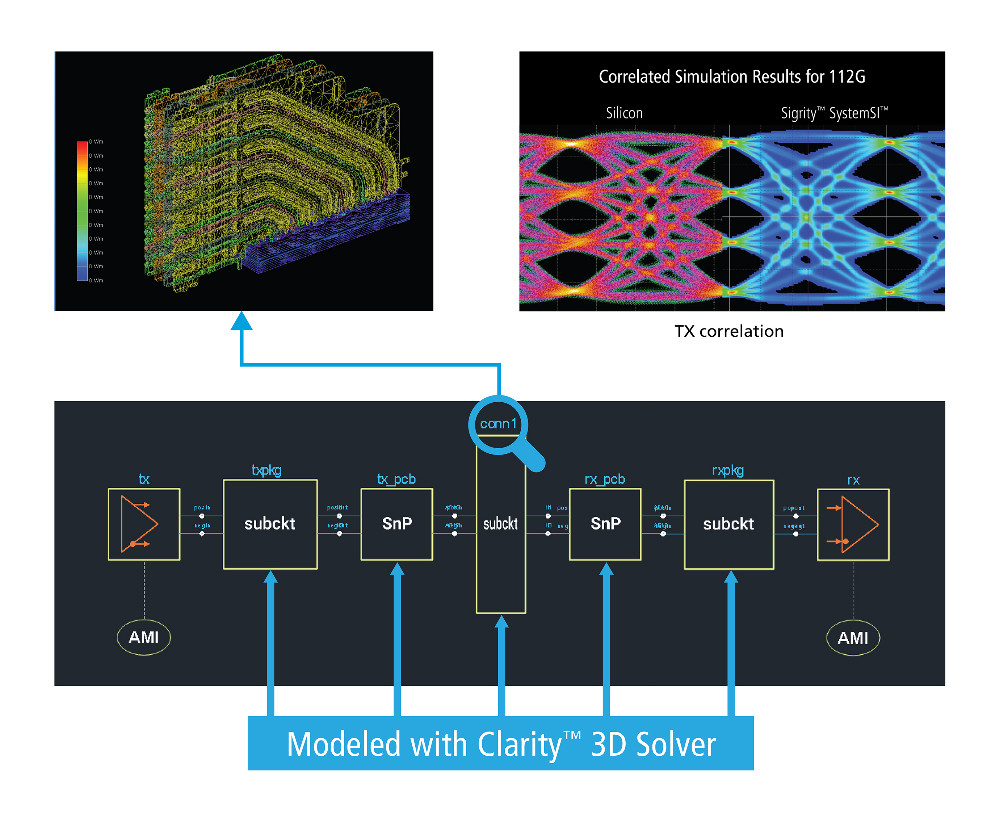

• Clarity 3D Solver场求解器是Cadence系统分析战略的首款产品,电磁仿真性能比传统产品提高10倍,并拥有近乎无限的处理能力,同时确保仿真精度达到黄金标准

• 全新的突破性的架构针对云计算和分布式计算的服务器进行优化,使得仿真任务支持调用数以百计的CPU进行求解

• 真正的3D建模技术,避免传统上为了提高仿真效率而人为对结构进行剪切带来的仿真精度降低的风险

• 轻松读取所有标准芯片和IC封装平台的设计数据,并与Cadence设计平台实现专属集成

- 关键字:

Cadence Cadence® Clarity™ 3D Solver场求解器

- 中国上海,2019年3月13日—Arm、Cadence Design Systems, Inc. (NASDAQ: CDNS)

和Xilinx, Inc. (NASDAQ: XLNX)今日宣布,联合推出基于全新ArmÒ Neoverse™

N1的系统开发平台,该平台将面向下一代云到边缘基础设施,并已在TSMC(TWSE: 2330, NYSE: TSM)

7纳米FinFET工艺上得到全面硅验证。Neoverse N1

系统开发平台(SDP)同时也是业内第一个7纳米基础设施开发平台,可利

- 关键字:

Arm Cadence Xilinx

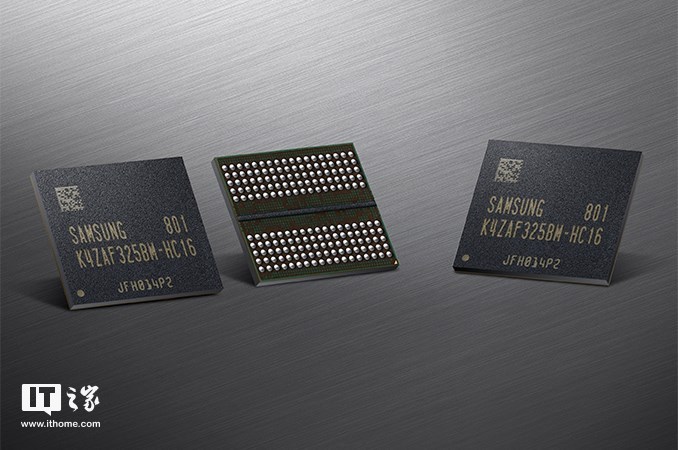

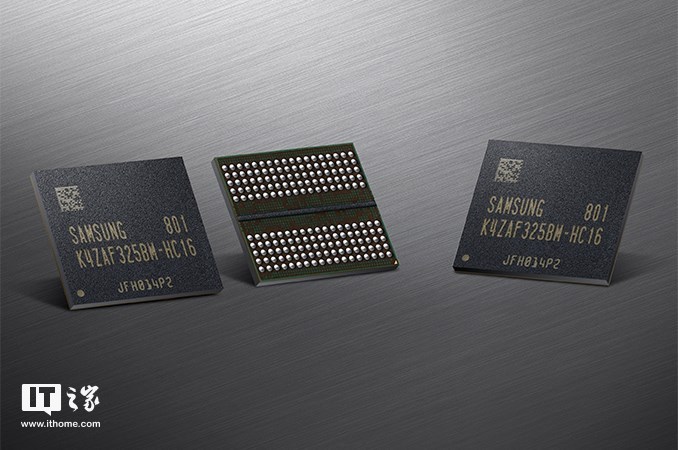

- 根据外媒报道,Cadence宣布已成功在三星的7LPP制造工艺中流片其GDDR6 IP芯片。 Cadence的GDDR6 IP解决方案包括该公司的Denali内存控制器,物理接口和验证IP。控制器和PHY的额定值可处理每个引脚高达16

Gbps的数据传输速率,并具有低误码率(BER)功能,可降低内存总线上的重试次数,从而缩短延迟,从而确保更大的内存带宽。IP封装以Cadence的参考设计提供,允许SoC开发人员快速复制IP设计人员用于其测试芯片的实现。 传统上,GDDR内存主要用于显卡,但

- 关键字:

Cadence GDDR6

- 移动多媒体领域的开发人员正努力应对行业飞速发展所带来的巨大机遇与挑战。日前,由MIPI联盟重要成员Cadence和泰克(Tektronix)联合举办的MIPI(Mobile

- 关键字:

MIPI Cadence Tektronix

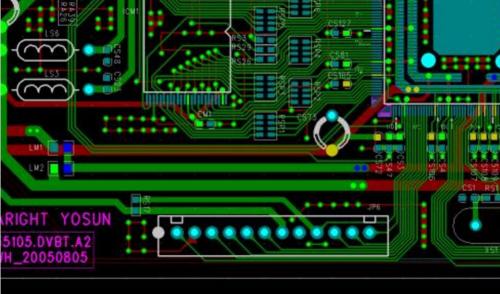

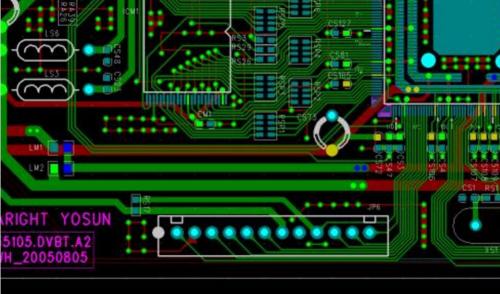

- 一、PCB工程师目前现状 近年来,随着工业4.0战略的实施,智能硬件的加速崛起,PCB工程师更是成为了未来最有前途的职业之一。特别是电子工业的不断壮大,使得产品研发周期不断缩短、信号速率不断提高、单板密度越来越大、门电路工作电压越来越低、SI-PI-EMI问题趋于复杂,这样就要求PCB设计工程师必须提高专业素养,也使得PCB设计的工作日益成为电子设计中独立而又不可缺失的一环。 二、作为一名Allegro工程师 面对电子设备这些高性能、高速、高密、轻薄的趋势,高速信号的PCB设计,越来越成为电子硬

- 关键字:

Cadence

- 随着芯片设计转移到90nm和65nm,芯片制造商面临着新的挑战包括温度、稳定性及电源可靠性或电源效率的差异性等方面的挑战。业界试图通过几种途径努力来

- 关键字:

EDA技术 芯片设计 Cadence

- 楷登电子(美国Cadence公司,NASDAQ: CDNS)今日宣布发布Cadence® Sigrity™ 2018版本,该版本包含最新的3D解决方案,帮助PCB设计团队缩短设计周期的同时实现设计成本和性能的最优化。 独有的3D设计及分析环境,完美集成了Sigrity工具与Cadence Allegro®技术,较之于当前市场上依赖于第三方建模工具的产品,Sigrity™ 2018版本可提供效率更高、出错率更低的解决方案,大幅度缩短设计周期的同时、降低设计失误风险。 此外,全新的3D Workbench

- 关键字:

Cadence,PCB

- 楷登电子(美国Cadence公司)今日宣布,瑞昱半导体股份有限公司(Realtek Semiconductor Corp.)将 Cadence® Innovus™ 设计实现系统用于其最新 28nm 数字电视(DTV)系统级芯片的研发并成功流片,同时成功缩小了芯片面积并降低了功耗。除了改善结果质量(QoR)之外,Innovus 设计实现系统容量更高,可支持实现更大的顶层模块,降低 SoC 顶层设计的分割区

- 关键字:

Cadence SoC

- PCB layout是什么 PCB layout是印刷电路板。 印刷电路板同时也叫印制电路板,是一种让各类电子元件实现有规则连接的载体。 PCB layout中文翻译为印制板布局,传统工艺上的电路板是利用印刷蚀刻出线路的方式,因此称之为印刷或印制电路板。利用印制板人们不仅能够避免安装过程接线错误(在PCB出现前,电子元件都是通过导线连接,不仅错综杂乱还存在安全隐患)。最早使用PCB的是一个奥地利人叫保罗。爱斯勒,于1936年首次在收音机中使用。广泛应用出现在20世纪

- 关键字:

Cadence PCB

- 楷登电子(美国Cadence公司)今日正式推出Cadence® Tensilica® Vision Q6 DSP。该DSP基于速度更快的新处理器架构,面向嵌入式视觉和AI技术量身打造。第五代Vision Q6 DSP的视觉和AI性能较上一代Vision P6 DSP提高达1.5倍,峰值性能下的功耗效率提高1.25倍。Vision Q6 DSP为智能手机、监控摄像头、汽车、增强现实(AR)/虚拟现实(VR

- 关键字:

Cadence Tensilica

cadence介绍

EDA仿真软件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473