楷登电子(美国Cadence公司)今日宣布,WillSemi采用CadenceÒ VirtuosoÒ 定制集成电路设计平台,增强了模拟集成电路设计的可靠性,并缩短了产品的总体上市时间。较此前部署的行业解决方案,WillSemi采用Cadence定制集成电路设计流程不仅将模拟设计和实现时间减半,总设计周期时间也缩短了三分之一。 Cadence定制设计流程工具帮助WillSemi集成电路设计团队实现了如下目标: · 采用Virtuoso电路原理图编辑器与Virtuoso版

关键字:

Cadence Virtuoso

封测大厂日月光2月1日召开法说会,展望2018年首季营运,日月光预期以美元计价的封测营收,将略高于去年同期12.3亿美元,毛利率将略高于去年同期的23%。电子代工(EMS)合并营收将略低于去年第三季331亿元,毛利率将略高于上季9.2%。

2017年日月光集团自结合并营收创2904.41亿元新台币新高,年增6%。毛利率18.2%、营益率8.7%,低于前年19.3%、9.7%。归属业主税后净利229.88亿元新台币,年增6%,创历史次高,受股本膨胀影响,每股盈余2.82元新台币,与前年追溯调整后相

关键字:

Cadence 存储器

楷登电子(美国Cadence 公司)今日宣布,业界首款支持全新 PCI Express ® (PCIe®)5.0 架构的验证 IP(VIP)正式可用。结合 TripleCheck™ 技术,Cadence® VIP 旨在帮助设计师快速执行基于 PCIe 5.0 标准的服务器和存储器的系统级芯片(SoC)设计的完整功能性验证,确保产品功能符合设计初衷。 如需进一步了

关键字:

Cadence IP

楷登电子(美国Cadence 公司, NASDAQ:CDNS)今日宣布,业界首款支持全新 PCI Express ® (PCIe®)5.0 架构的验证 IP(VIP)正式可用。结合 TripleCheck™ 技术,Cadence® VIP 旨在帮助设计师快速执行基于 PCIe 5.0 标准的服务器和存储器的系统级芯片(SoC)设计的完整功能性验证,确保产品功能符合设计初衷。

如需进一步了解基于PCIe 5.0架构并采用TripleCheck技术的Cadence

关键字:

Cadence PCI

中国的半导体产业持续呈现超过20%的成长率,而全球只有约5%。在中国建立本土化的公司,这对Cadence来说是个很重要的决定,从一年前开始讨论这个问题,最后决定选址南京...

2017年11月13日,江苏南京,Cadence与南京市浦口区人民政府签署了为建立Cadence (中国)半导体产业基地的战略合作备忘录及中国IC知识产权(IP)开发与服务平台的正式投资协定。

此次签约仪式受到中国半导体业界的广泛关注,100多位嘉宾现场出席和见证了仪式。

江苏省省委常委、南京市市委书记张敬华代

关键字:

Cadence EDA

11月13日,电子设计自动化(EDA)与半导体知识产权(IP)的领先供应商美国楷登电子(Cadence)与南京市浦口区人民政府正式签署战略合作备忘录以及投资协议。据悉,Cadence 项目是南京市浦口区继引进台积电之后在集成电路设计领域引进的又一个龙头性项目,历经两年的洽谈,在多方的共同努力下,今天终于签约落地。

南京市江北新区管委会常务副主任、浦口区区委书记瞿为民先生致辞表示,此次签约仪式标志着南京市浦口区与 Cadence 双方的战略投资进入实质性阶段。南京江北新区是江苏省唯一的国家级新区,

关键字:

Cadence 台积电

楷登电子(美国Cadence 公司)今日与Arm联合发布基于Arm® 服务器的Xcelium™ 并行逻辑仿真平台,这是电子行业内首个低功耗高性能的仿真解决方案。 在芯片制造之前, SoC芯片功能正确性验证占用了整个项目70%的EDA软件使用资源,这一需求促进了数据中心的增长。运行于ARM服务器的Xcelium仿真可带来功耗显著降低和仿真容量的显著提升,可执行高吞吐和长周期测试,缩减了整个SoC验证的时间和成本。 作为Cadence验证套件(Cadence&n

关键字:

Cadence Xcelium

楷登电子(美国Cadence公司)今日宣布,其全流程数字签核工具和Cadence® 验证套装的优化工作已经发布,支持最新Arm® Cortex®-A75和Cortex-A55 CP,基于Arm DynamIQ™技术的设计,及Arm Mali™-G72 GPU,可广泛用于最新一代的高端移动应用、机器学习及消费电子类芯片。为加速针对Arm最新处理器的设计,Cadence为Cortex-A75和Cortex-A55 CPU量身开发全新7n

关键字:

Cadence Arm

楷登电子(美国Cadence公司)宣布即将于8月22日(星期二)在上海浦东嘉里大酒店举办一年一度的中国用户大会——CDNLive China 2017。以“联结,分享,启发!”为主题的CDNLive大会将集聚超过1000位IC行业从业者,包括IC设计工程师、系统开发者与业界专家,将分享重要半导体设计领域的解决方案和成功经验,让参与者获得知识、灵感与动力,并为实现高阶半导体芯片、SoC设计和系统挑战提供解决方案。详细的会议信息及报名请浏览www.cdnlive.com CDNLiv

关键字:

Cadence CDNLive

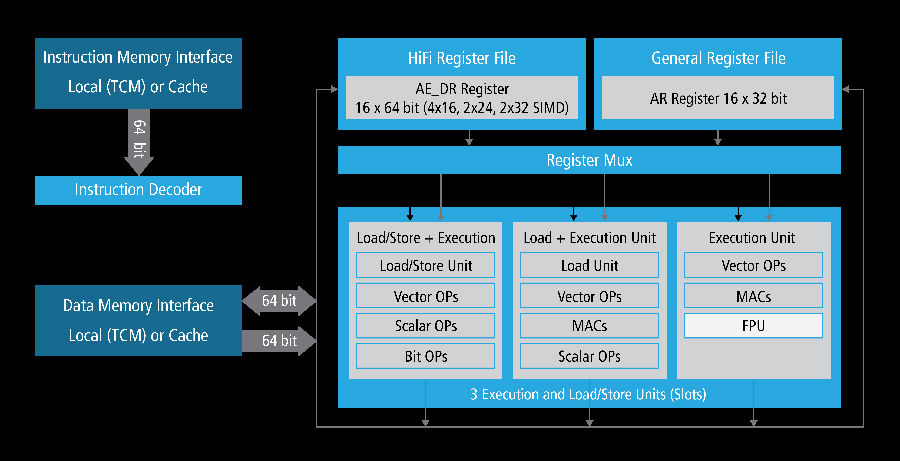

楷登电子(美国 Cadence 公司)今天宣布推出针对最新移动和家庭娱乐应用中系统级芯片(SoC)设计的Cadence® Tensilica® HiFi 3z DSP IP内核 。其应用包括智能手机、增强现实(AR)/ 3D眼镜、数字电视和机顶盒(STB)等。比较在业界音频DSP内核发货量站主导地位的前一代产品HiFi 3 DSP ,新的HiFi 3z架构将可提供超过1.3

关键字:

Cadence DSP

做芯片设计的各位,在某个时刻,你也许会产生一个想法,“为什么不自己设计一个处理器呢?”或许是手头的处理器并不好用;或许是想用的处理器贵的离谱;或许是你希望做出差异化的产品;又或者仅仅因为它是个诱人的挑战,你想尝试一下...既然如此,我很高兴能和你讨论一下怎么完成这个任务。 交付物 我们先从结果说起,也就是这项任务的最终交付物。这里不妨参考ARM处理器核的deliverables。当然,如果只是一个自己用的专用处理器,不一定要有这么完整的交付物。 硬件:主要是处理器相关的RTL代码,验证环境,ED

关键字:

专用处理器 Cadence

楷登电子(美国Cadence公司)今日正式发布全新VirtualBridge™适配器。较传统RTL仿真,基于虚拟仿真技术的VirtualBridge™适配器可以加速硅前验证阶段的软件初启。同时,VirtualBridge适配器与传统在线(In-Circuit)仿真应用模式互为补充,通过Cadence® Palladium® Z1企业级仿真平台,可以让软件设计师提前3个月开始进行硅前软件验证工作。如需了解更多内容,请访问www.cadence.com/go/virtualbridge

关键字:

Cadence VirtualBridge

楷登电子(美国Cadence公司)今日发布全新Cadence® Virtuoso® System Design Platform(Virtuoso系统设计平台),结合Cadence Virtuoso平台与Allegro® 及Sigrity™技术,打造一个正式的、优化的自动协同设计与验证流程。多项跨平台技术的高度集成帮助设计工程师实现芯片、封装和电路板的同步和协同设计。这一过程在此之前只能通过手动完成,全新Virtuoso系统设计平台可以实现流

关键字:

Cadence Virtuoso

楷登电子(美国Cadence公司)今日正式发布JasperGold® 形式验证平台扩展版,引入高级形式化验证技术的JasperGold Superlint和Clock Domain Crossing (CDC)应用,以满足JasperGold形式验证技术在RTL设计领域的签核要求。较现有验证解决方案,Superlint和CDC应用提高了IP设计质量,后期RTL变更最高减少80%, IP开发时间缩短4周。如需了解更多关于JasperGold技术

关键字:

Cadence RTL

楷登电子(美国 Cadence 公司) 今日宣布其数字、签核与定制/模拟工具成功在三星电子公司7LPP和8LPP工艺技术上实现。较前代高阶工艺节点FinFET技术,7LPP和8LPP工艺技术不仅进一步优化了功耗、性能和面积特性,扩展能力也更为出色。目前,客户已经可以应用下一代技术开始早期设计。 Cadence定制/模拟、数字和签核工具全面满足三星工艺需求,支持实现7LPP和8LPP工艺技术;三星客户可开发各类复杂的高阶节点设计,充分满足移动市场和其他垂直市场的应用需求。

关键字:

Cadence 7LPP

cadence介绍

EDA仿真软件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473